1 setup phase, Chart – Texas Instruments TMS320DM357 User Manual

Page 45

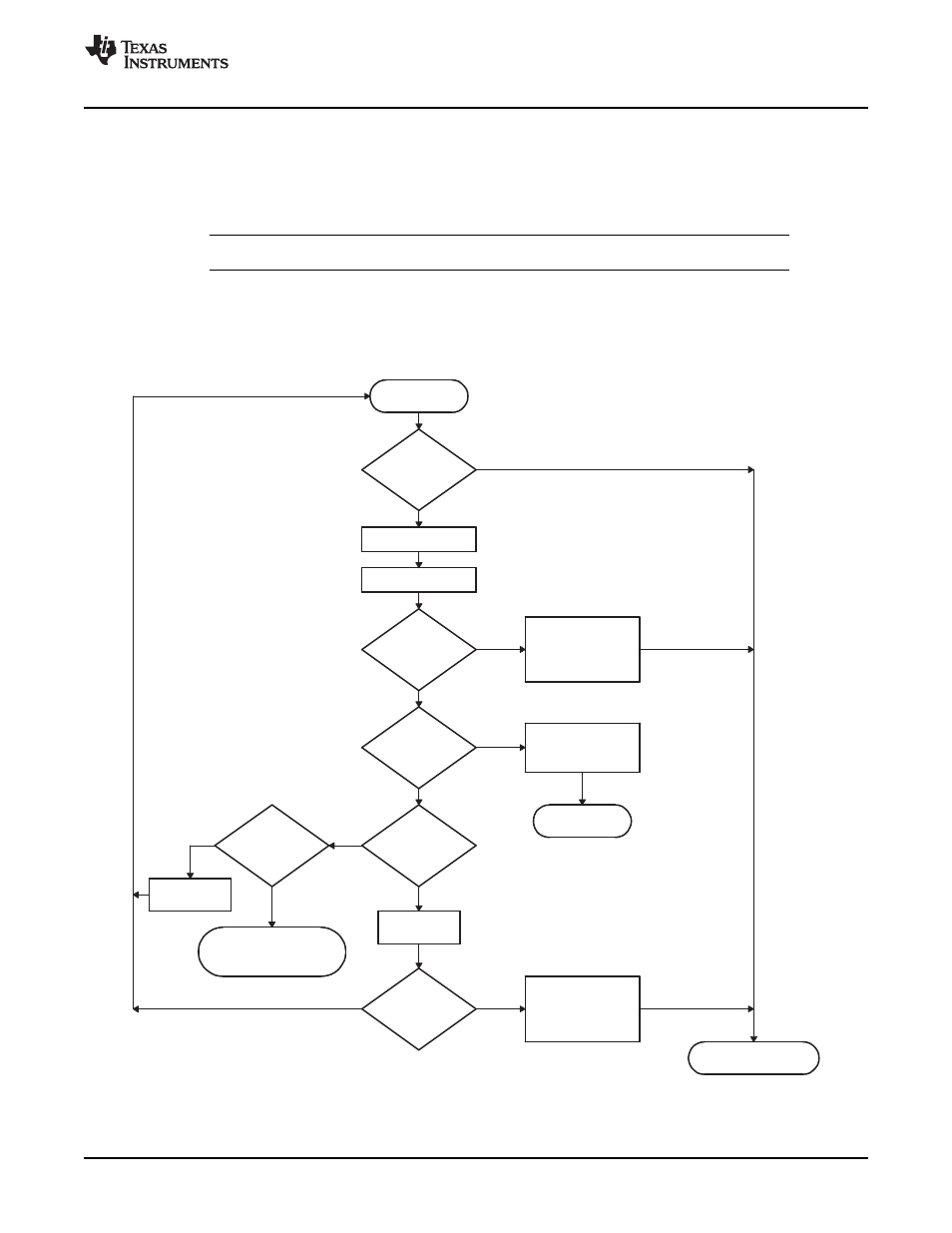

3.2.1.1

Setup Phase

Transaction

scheduled

TxPktRdy

and SetupPkt

both set

?

SETUP token sent

DATA0 oacket sent

?

received

Stall

No

Yes

Yes

No

RxStall set

TxPktRdy cleared

Error Count cleared

interrupt generated

Command not

supported by

target

TxPktRdy cleared

Error Count cleared

Interrupt generated

Yes

?

No

ACK

received

Transaction

complete

No

NAK

received

?

Yes

?

NAK limit

reached

No

Yes

Error count

cleared

incremented

Error count

NAK Timeout set

Endpoint halted

Interrupt generated

?

Error

count=3

No

Error bit set

TxPktRdy cleared

Error Count cleared

interrupt generated

Yes

Implies problem

at peripheral end

of connection.

Transaction deemed

complete

www.ti.com

USB Controller Host and Peripheral Modes Operation

For the SETUP Phase of a control transaction (

), the software driving the US host device needs

to:

1. Load the 8 bytes of the required Device request command into the Endpoint 0 FIFO.

2. Set SETUPPKT and TXPKTRDY (bits 3 and 1 of HOST_CSR0, respectively).

Note:

These bits must be set together.

The controller then proceeds to send a SETUP token followed by the 8-byte command to Endpoint 0 of

the addressed device, retrying as necessary. (On errors, controller retries the transaction three times.)

Figure 9. Setup Phase of a Control Transaction Flow Chart

SPRUGH3 – November 2008

Universal Serial Bus (USB) Controller

45