3 interface control signals, Table 3.3 chip interface control signals, Interface control signals – Avago Technologies LSI53C320 User Manual

Page 39: Chip interface control signals

Interface Control Signals

3-5

Version 2.2

Copyright © 2003 by LSI Logic Corporation. All rights reserved.

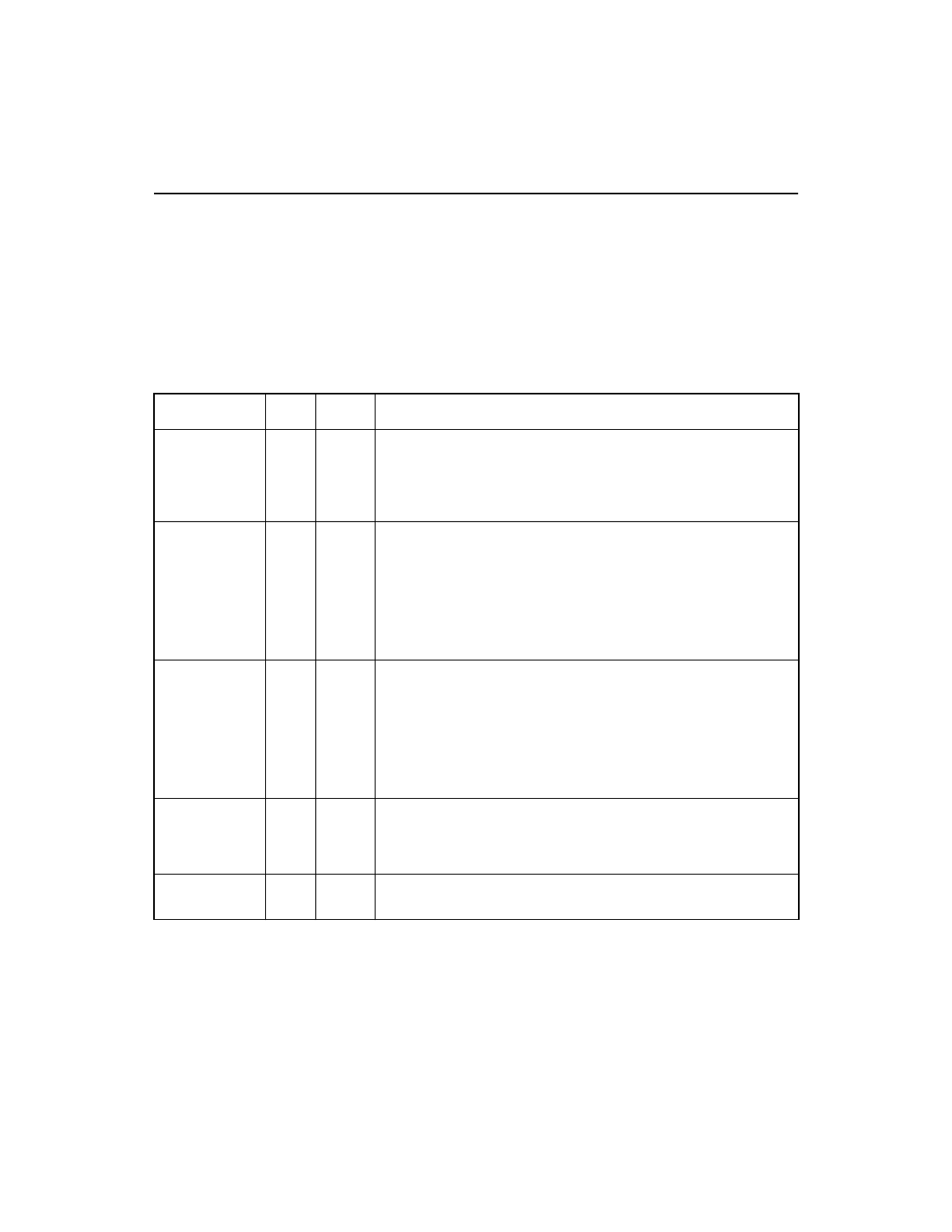

3.3 Interface Control Signals

describes the interface control signals for the LSI53C320. The

LSI53C320 requires an external POR, which is implemented using the

CHIP_RESET/ signal.

provides an example external POR

circuit.

Table 3.3

Chip Interface Control Signals

Signal Name

Pin

Type

Description

CHIP_RESET/

C10

I

The active LOW Master Reset signal provides a general purpose

chip reset that forces the internal elements of the LSI53C320 to a

known state. Asserting this signal places the LSI53C320 state

machine in an idle state and places all controls in a passive state.

The minimum CHIP_RESET/ asserted pulse width is 100 ns.

WS_ENABLE/

A7

I

The Active LOW Warm Swap Enable signal enables and disables

SCSI transfers through the LSI53C320. The WS_ENABLE/ input

removes the chip from an active bus without disturbing the current

SCSI transaction. When Warm Swap Enable asserts, the

LSI53C320 3-states the SCSI signals after it detects the next bus

free state. The LSI53C320 no longer passes on signals until the

WS_ENABLE/ pin deasserts and both SCSI buses enter the Bus

Free state.

XFER_ACTIVE

A8

O

The Transfer Active signal enables and disables SCSI transfers

through the LSI53C320. The LSI53C320 asserts this signal when

the chip is active to indicate that the chip completed its internal

testing, the SCSI bus has entered a bus free state, or that SCSI

traffic can now pass from one side of the chip to the other side of

the chip. The LSI53C320 deasserts this signal to detect a Bus

Free state due to the WS_ENABLE/ signal being LOW.

Deasserting this signal disables transfers through the device.

CLOCK

A9

I

CLOCK provides the 40 MHz oscillator input to the LSI53C320. It

is the clock source for the protocol control state machines and

timing generation logic. The bus signal transfer paths do not use

this clock.

BSY_LED

B9

O

The Busy LED signal provides an 8 mA SCSI activity LED output.

The LSI53C320 asserts this signal to indicate SCSI bus activity.