Sundance SMT310Q User Manual

Page 41

Version 2.1

Page 41 of 55

SMT310Q User Manual

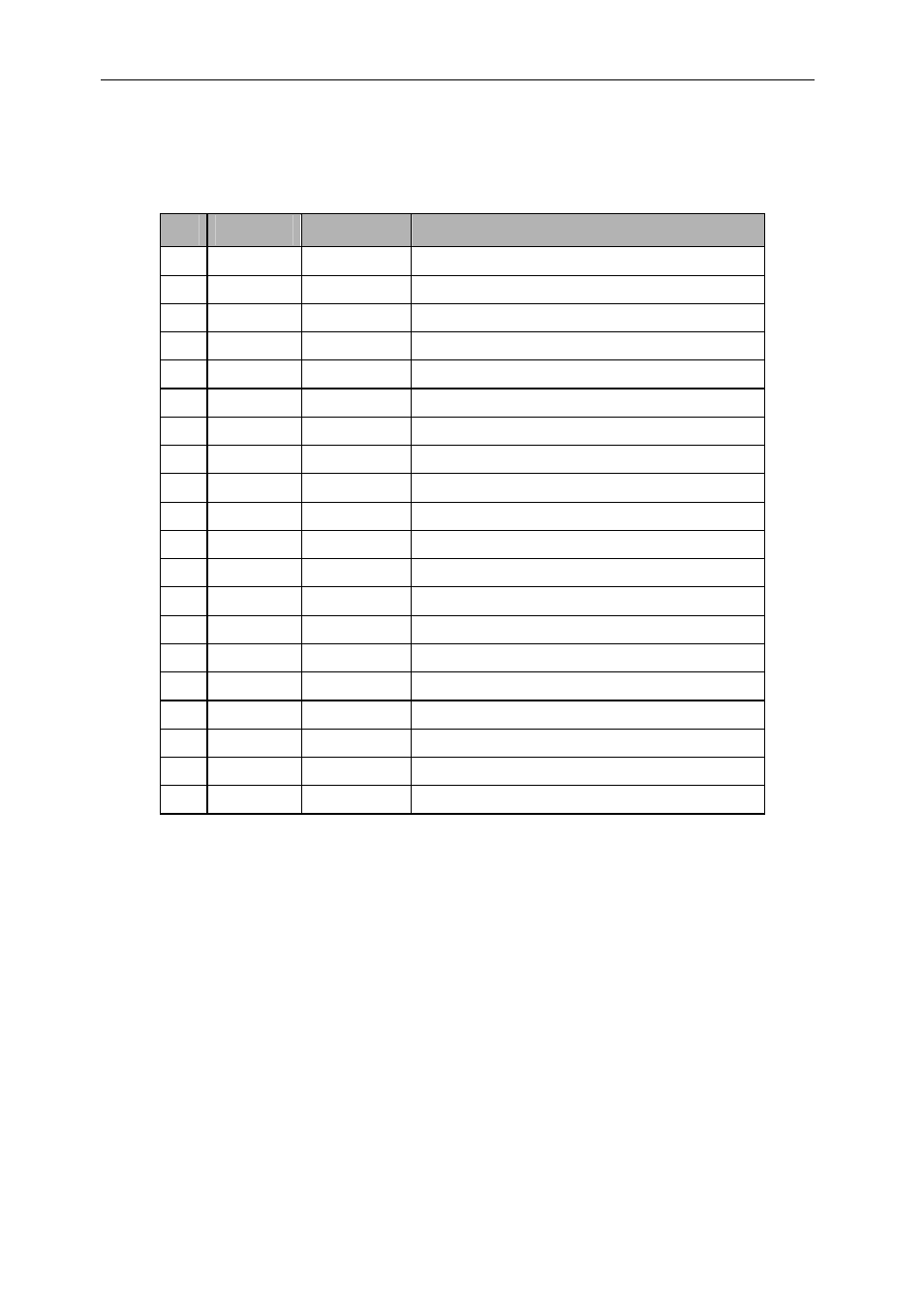

When the SMT310Q is configured as a Slave using the Buffered JTAG

connector as a JTAG source, the buffered connector pins are used as follows:

Pin

Signal

Direction

Description

1

TDI

IN

JTAG data in

2 GND

3

TDO

OUT

JTAG data out

4 GND

5

TMS

IN

JTAG Test mode select

6 GND

7

TCK

IN

JTAG clock, up to 10MHz

8 GND

9

TCK_RET

OUT

JTAG clock return

10 GND

11 /TRST

IN

JTAG

Reset

12 GND

13 /RESET

IN

Board

Reset

in

14

PD

OUT

Presence detect, +5V 1A fused

15

/DETECT

IN

Detect external JTAG controller when grounded

16

CONFIG

OPEN COLL

Global open collector C4x CONFIG

17

EMU0

OUT

Buffered EMU0 output

18

EMU1

OUT

Buffered EMU1 output

19 SPARE1

20 SPARE2

Table 14: Buffered JTAG connector pin functionality as JTAG source