3 status register (bar1, offset 1416, read-only), Status register (bar1, offset 14, Read-only) – Sundance SMT310Q User Manual

Page 18: 3 status register (bar1, offset 14

Version 2.1

Page 18 of 55

SMT310Q User Manual

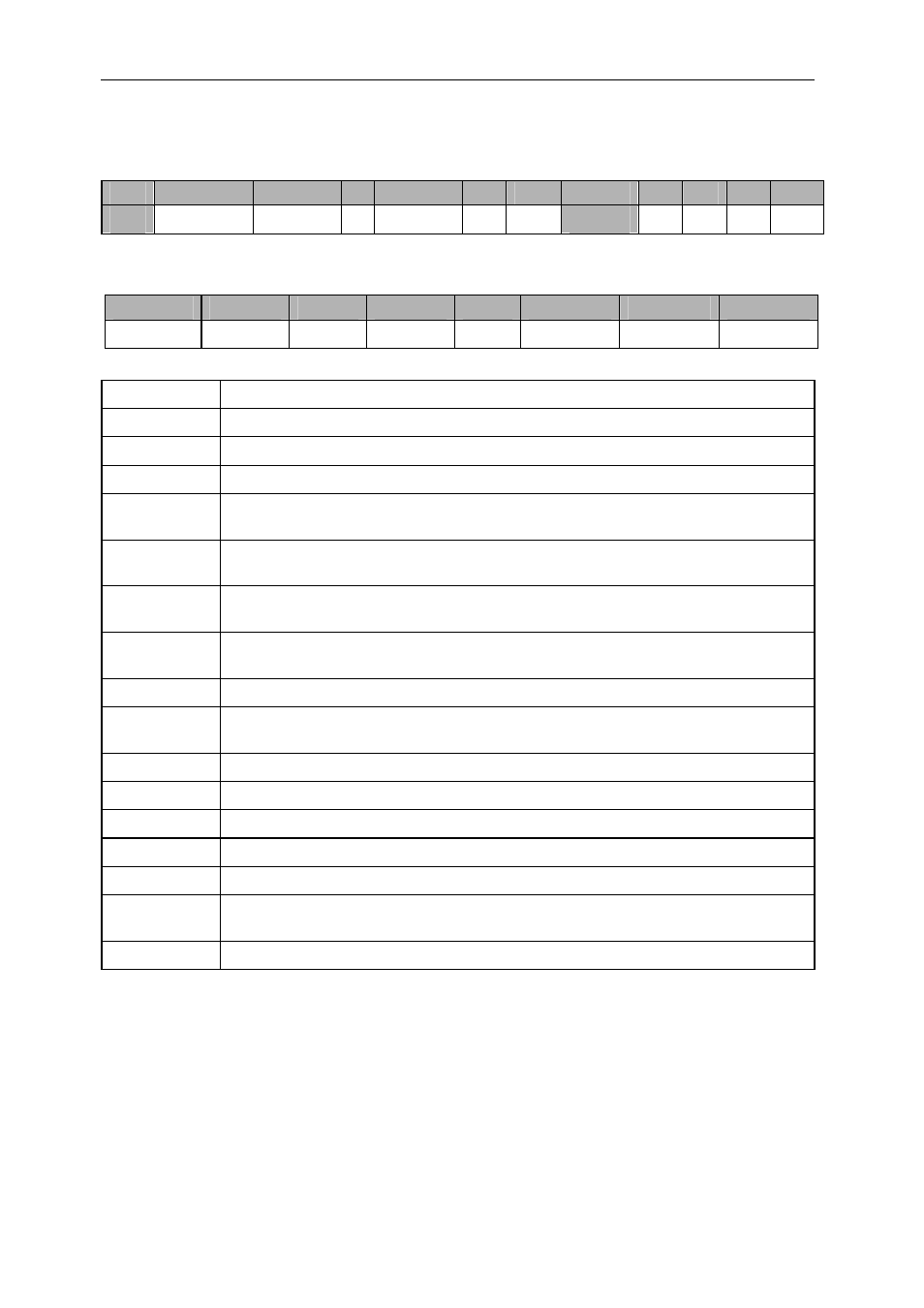

4.3.3 Status Register (BAR1, Offset 14

16

, Read-Only)

31-22

21

20

19

18

17

16

15-12

11

10

9

8

CONFIG_L

TBC

RDY

0

MASTER

IBF

OBF IM2

IM1

IM0

INTD

7

6

5

4

3

2

1

0

C40 INT

TBC INT

IBF INT

OBE INT

C40 IE

TBC IE

IBF IE

OBE IE

OBE IE

Set if comport output buffer empty interrupts enabled.

IBF IE

Set if comport input buffer full interrupts enabled

TBC IE

Set if JTAG interrupts enabled

C40 IE

Set if interrupt from TIM DSP enabled

OBE INT

Set if the comport output buffer becomes empty. Cleared by writing a 1 to the

corresponding bit in the interrupt control register.

IBF INT

Set if the comport input buffer receives a word. Cleared by writing a 1to the

corresponding bit in the interrupt control register

TBC INT

Set when the TBC asserts its interrupt. Cleared by removing the source of the

interrupt in the TBC.

C40 INT

Set when the TIM DSP sets its host interrupt bit. Cleared by writing a 1 to the

corresponding bit in the interrupt control register.

INTD

The logical OR of bits 7—4 in this register gated with each one’s enable bit.

OBF

Set when a word has been written to the comport output register. Cleared when the

word has been transmitted to the DSP.

IM0

Interrupt mask 0. Returns Interrupt Control Register Bit 8.

IM1

Interrupt mask 1. Returns Interrupt Control Register Bit 9.

IM2

Interrupt mask 2. Returns Interrupt Control Register Bit 10.

IBF

Set when a word has been received into the comport input register.

MASTER

Set when the SMT310Q bridge owns the comport interface token.

TBC RDY

Reflects the current state of the TBC RDY pin. This bit is active high and therefore

is an inversion of the TBC pin.

CONFIG_L

Reflects the state of the TIMs’ CONFIG signal. Active low.

Table 4: Status Register

INTD is the input interrupt into the PCI Bridge from the SMT310Q; this can be

routed to INTA, INTB, or INTC using the PCI Interrupt Configuration Register

(BAR0, offset 4C

16

).