3 memory space assignments (bar2), 4 dma engine, Memory space assignments (bar2) – Sundance SMT310Q User Manual

Page 33: Dma engine

Version 2.1

Page 33 of 55

SMT310Q User Manual

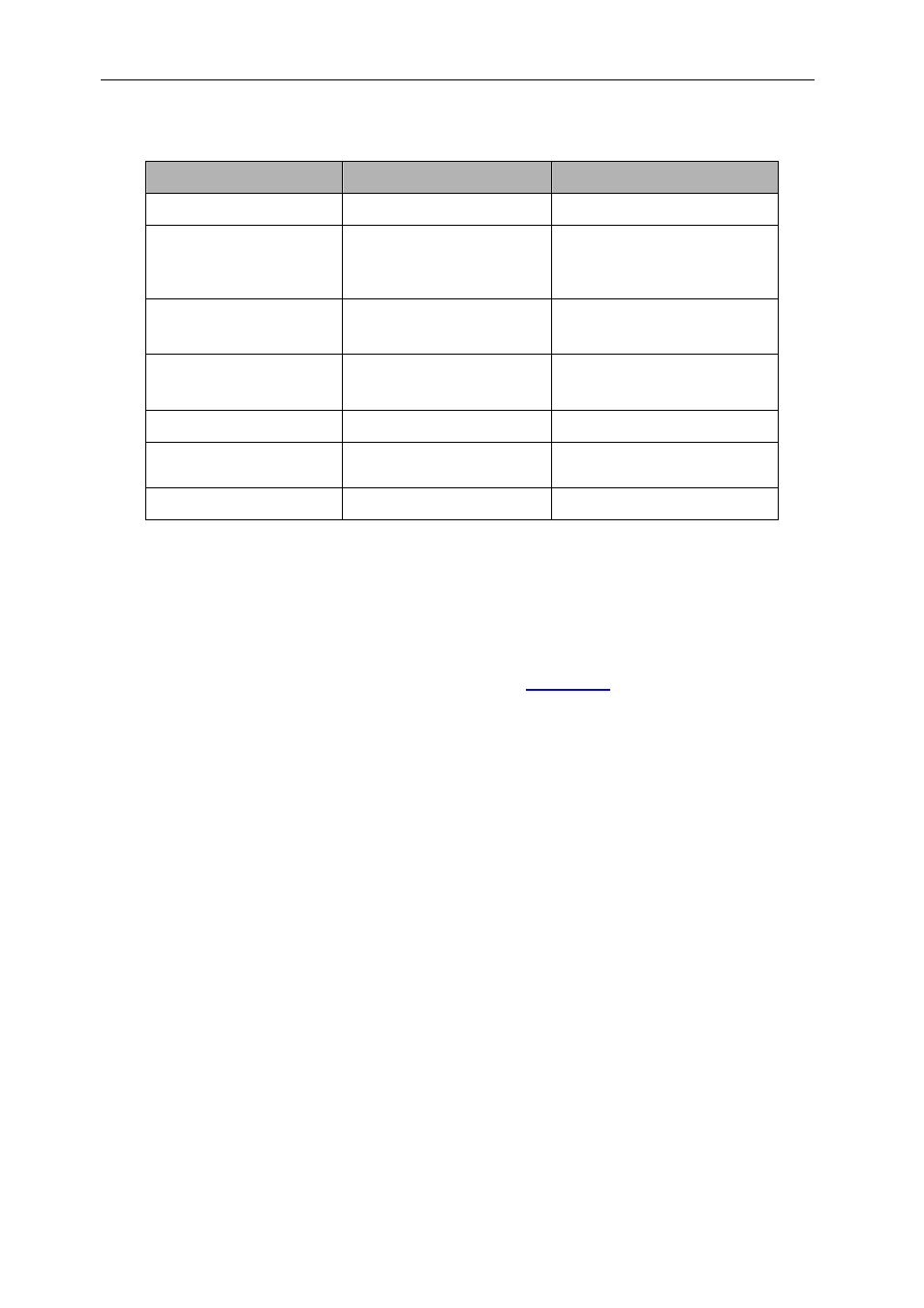

9.1.3 Memory Space Assignments (BAR2)

Address

Description

Notes

00000000

16

–000FFFFF

16

Shared Memory Bank

1MB SRAM

00200090

16

Comport Data Mirror

Mirror of COMPORT_OUT /

COMPORT_IN

See Note 2

00200094

16

Comport Status Mirror

Mirror of Control / Status

See Note 2

00200098

16

Comport Int_Control Mirror

Mirror of Int_Control

See Note 2

00200000

16

–0020007F

16

Global Bus

See Note 1

00200240

16

–0020 025F

16

SDB Data Register

Input/Output 16 bit SDB

Interface

00200260

16

–0020027F

16

SDB Control Register

SDB Control/Status

Table 9: Memory space map

Note 1: In order for the TIM to respond to accesses for this area address line

GADD30 and GADD19 of the TIM site connector must be decoded as high

and GADD7 and GADD5 must be decoded as low.

Note 2: These mirrors of addresses in the

(BAR1) allow increased

transfer speeds across the host comport link (in excess of ×10 increase).

9.1.4 DMA Engine

The PCI Bridge DMA processor sees the shared memory at a different

address from that used for normal accesses. For normal memory access the

memory base address register offset is 00000000

16

. For DMA access address

line A28 (On hardware interface) must be high, therefore DMA memory access

starts at 40000000

16

(not 10000000

16

as addressing is in bytes).