I/o & serial i/o, 10/100 ethernet, I/o & serial i/o –8 – Altera Cyclone II EP2C35 PCI Development Board User Manual

Page 42

4–8

Core Version 4.0.0

Altera Corporation

Cyclone II EP2C35 PCI Development Board Reference Manual

May 2005

I/O & Serial I/O

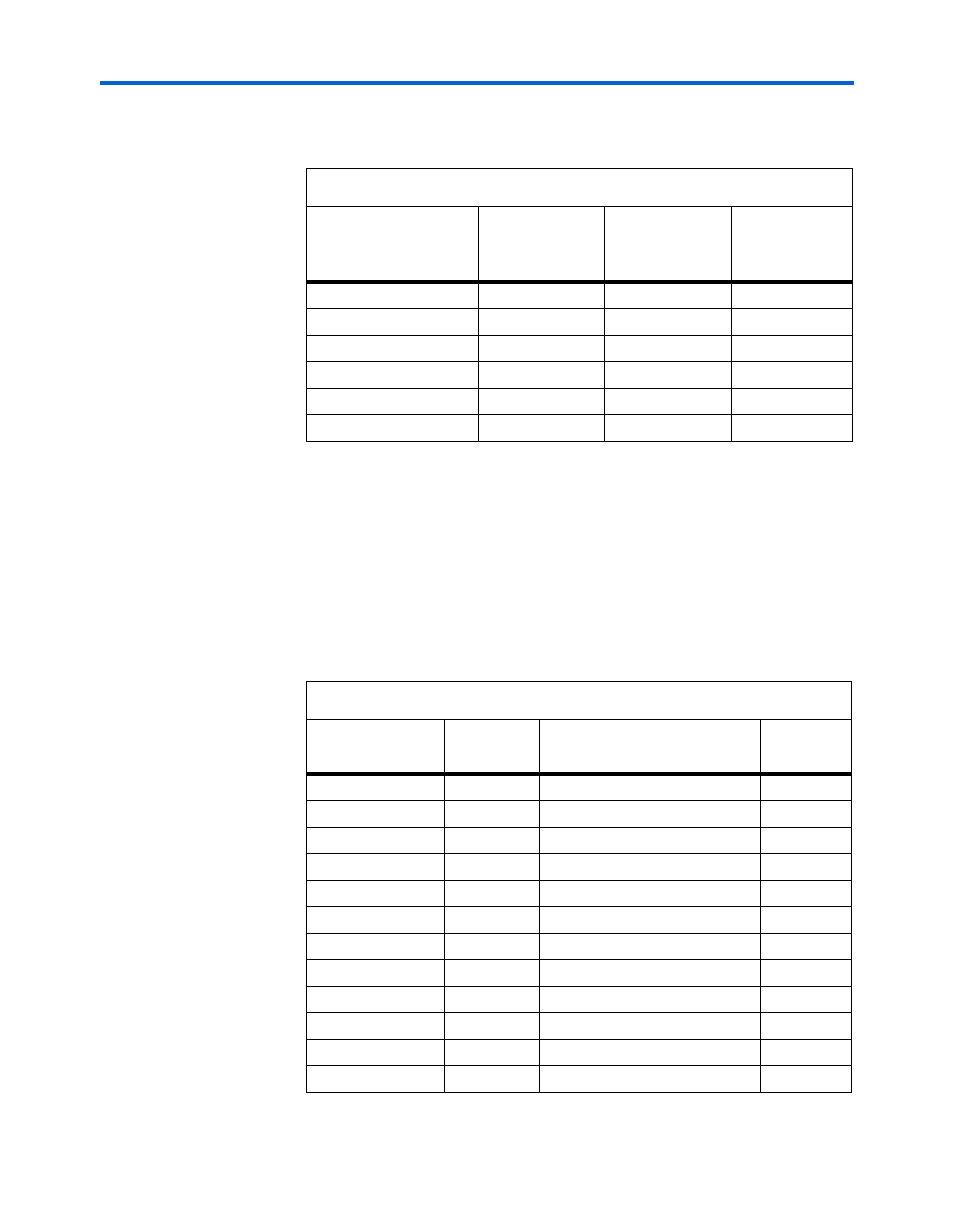

Table 4–4

shows the DDR2 SDRAM memory clock signal connections.

I/O & Serial I/O

This section describes signal specifications for the following interfaces:

■

10/100 Ethernet

■

RS-232 serial interface

10/100 Ethernet

shows the 10/100 Ethernet interface signal connections.

Table 4–4. DDR2 SDRAM Memory Clock Signal Connections

Clock Signal

DDR2 SDRAM

Memory

Device 1 (U6)

DDR2 SDRAM

Memory

Device 1 (U10)

Cyclone II Pin

(U9)

DDR2_CK_N0

–

K8

A23

DDR2_CK_P0

–

J8

A22

DDR2_CK_N1

K8

–

A8

DDR2_CK_P1

J8

–

A9

DDR2_SYNC_CLK_IN

–

–

AF14

DDR2_SYNC_CLK_OUT

–

–

B7

Table 4–5. 10/100 Ethernet Interface Signal Connections (Part 1 of 3)

Ethernet Signal

Connector

Pin (RJ1)

MAC/PHY Pin (U3)

Cyclone II

Pin (U9)

LAN_TXDp

RJ1.1

U3.14

–

LAN_TXDn

RJ1.3

U3.15

–

LAN_RXDp

RJ1.4

U3.17 (through resistor R49)

–

LAN_RXDn

RJ1.6

U3.18 (through resistor R53)

–

LAN_LEDA_n

RJ1.10

U3.22

–

LAN_LEDB_n

RJ1.12

U3.23

–

LAN_BEn0

–

U3.94

U5

LAN_BEn1

–

U3.95

U6

LAN_BEn2

–

U3.96

U7

LAN_BEn3

–

U3.97

V1

LAN_AEN

–

U3.41

V4

LAN_A1

–

U3.78

V7