Output ports – Altera Virtual JTAG IP Core User Manual

Page 11

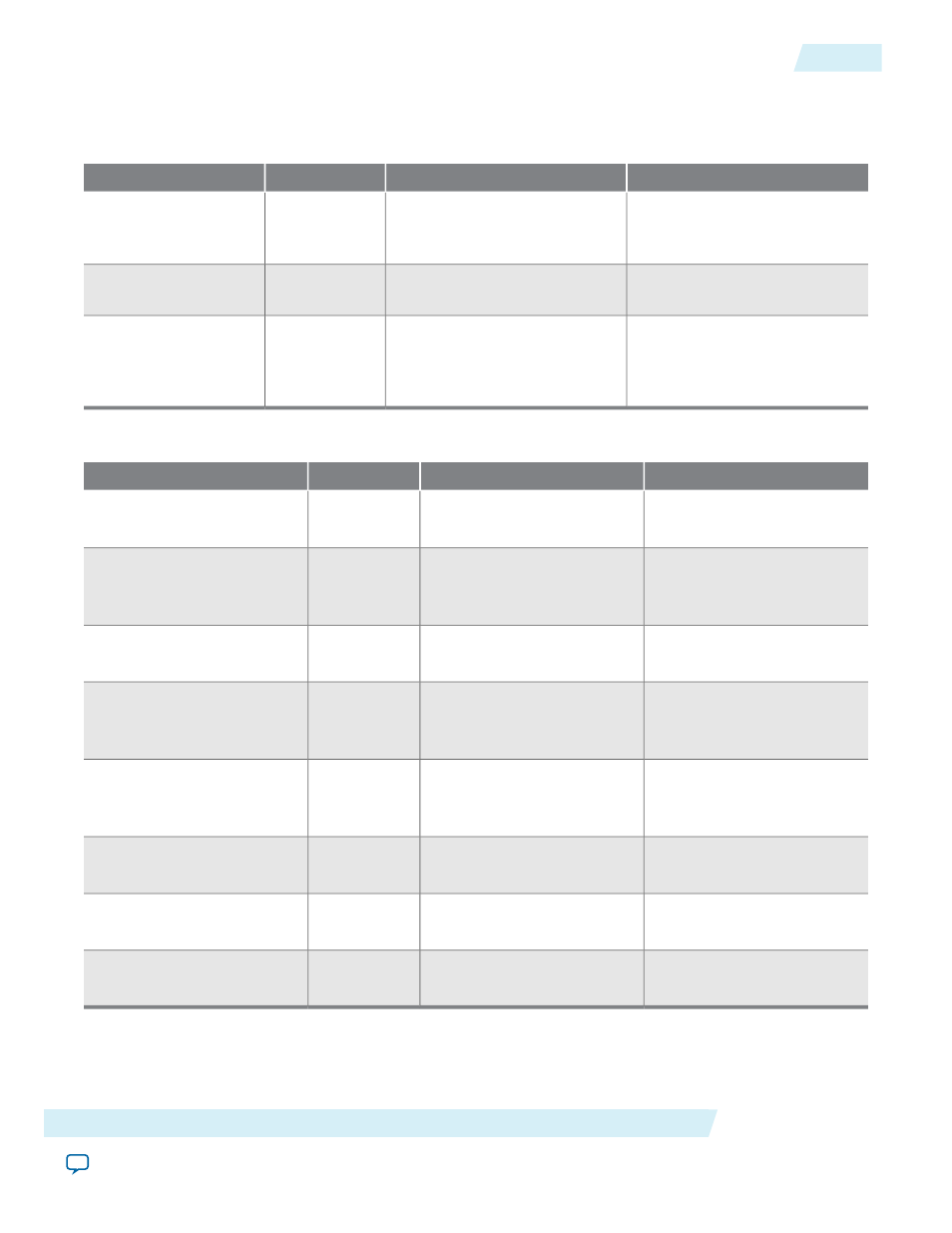

Output Ports

Table 3: Output Ports for the Virtual JTAG Megafunction

Comments

Description

Required

Port Name

Connected directly to the

TCK

device pin. Shared among all

virtual JTAG instances.

JTAG test clock.

Yes

tck

Shared among all virtual JTAG

instances.

TDI input data on the device. Used

when

virtual_state_sdr

is high.

Yes

tdi

Output port

[SLD_IR_WIDTH-

1..0]

wide. Specify the width

of this bus with the

SLD_IR_

WIDTH

parameter.

Virtual JTAG instruction register

data. The value is available and

latched when

virtual_state_uir

is high.

No

ir_in[]

Table 4: High-Level Virtual JTAG State Signals

Comments

Description

Required

Port Name

Indicates that virtual JTAG is in

Capture_DR state.

No

virtual_state_cdr

In this state, this instance is

required to establish the

JTAG chain for this device.

Indicates that virtual JTAG is in

Shift_DR state.

Yes

virtual_state_sdr

Indicates that virtual JTAG is in

Exit1_DR state.

No

virtual_state_e1dr

The Quartus II software does

not cycle through this state

using the Tcl command.

Indicates that virtual JTAG is in

Pause_DR state.

No

virtual_state pdr

The Quartus II software does

not cycle through this state

using the Tcl command.

Indicates that virtual JTAG is in

Exit2_DR state.

No

virtual_state_e2dr

Indicates that virtual JTAG is in

Update_DR state.

No

virtual_state_udr

Indicates that virtual JTAG is in

Capture_IR state.

No

virtual_state_cir

Indicates that virtual JTAG is in

Update_IR state.

No

virtual_state_uir

Altera Corporation

Virtual JTAG Megafunction (sld_virtual_jtag)

11

Output Ports

UG-SLDVRTL

2014.03.19