Dsp ip core verification, Fir ii ip core release information, Dsp ip core verification -3 – Altera FIR Compiler II MegaCore Function User Manual

Page 6: Fir ii ip core release information -3

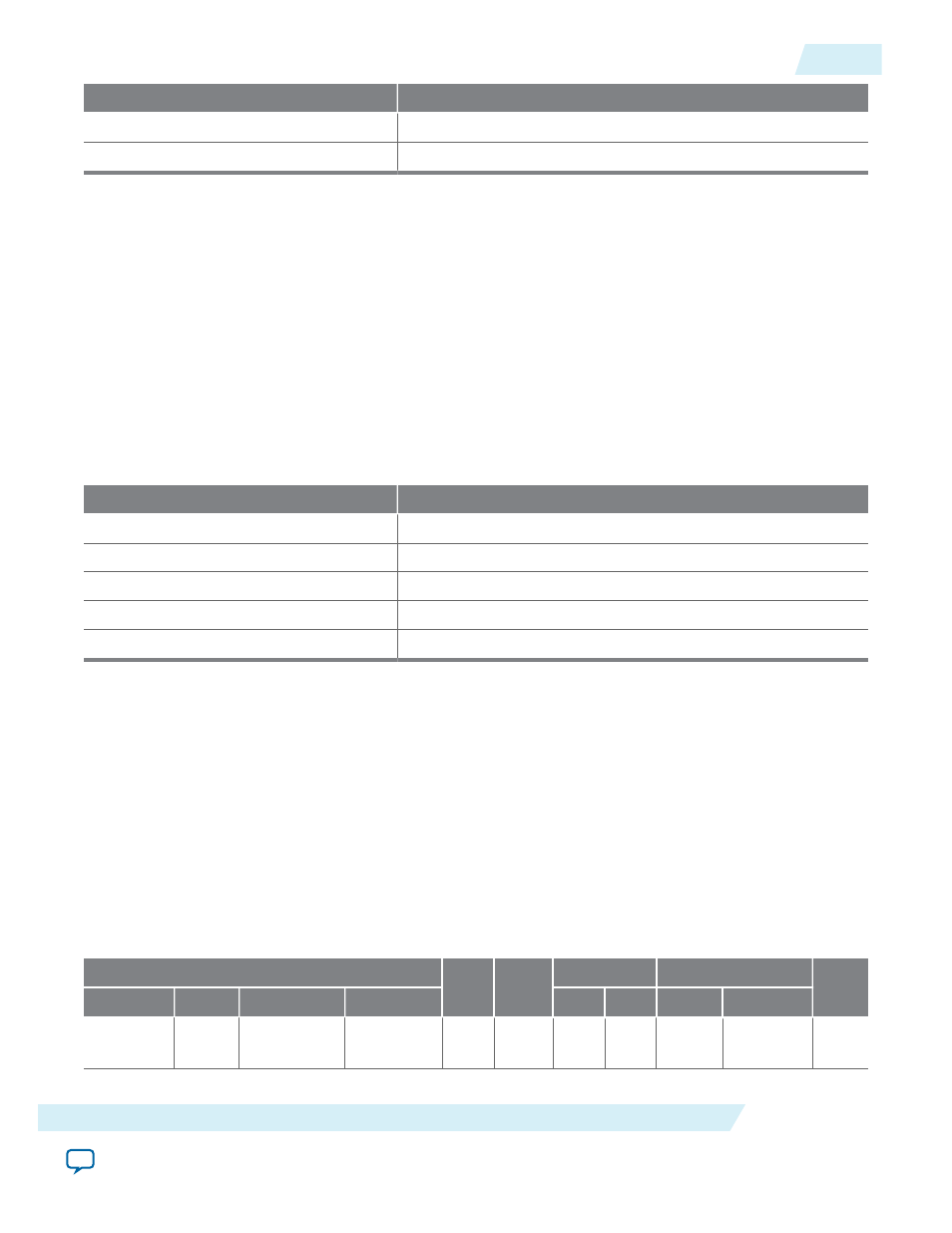

Device Family

Support

Stratix V

Final

Other device families

No support

DSP IP Core Verification

Before releasing a version of an IP core, Altera runs comprehensive regression tests to verify its quality

and correctness. Altera generates custom variations of the IP core to exercise the various parameter

options and thoroughly simulates the resulting simulation models with the results verified against master

simulation models.

FIR II IP Core Release Information

Use the release information when licensing the IP core.

Table 1-2: Release Information

Item

Description

Version

14.1

Release Date

December 2014

Ordering Code

IP-FIRII

Product ID

00D8

Vendor ID

6AF7

Altera verifies that the current version of the Quartus II software compiles the previous version of each IP

core. Altera does not verify that the Quartus II software compiles IP core versions older than the previous

version. The Altera IP Release Notes lists any exceptions.

Related Information

•

•

FIR II IP Core Performance and Resource Utilization

Table 1-3: FIR II IP Core Performance—Arria V Devices

Typical expected performance using the Quartus II software with Arria V (5AGXFB3H4F40C4).

Parameters

ALM

DSP

Blocks

Memory

Registers

f

MAX

(MHz)

Channel

Wires

Filter Type

Coefficients

M10K M20K Primary Secondary

8

2

Decimation

—

1,607 24

0

—

1,232

64

30

8

UG-01072

2014.12.15

DSP IP Core Verification

1-3

About the FIR II IP Core

Altera Corporation