Fir ii ip core multichannel operation, Vectorized inputs, Fir ii ip core multichannel operation -12 – Altera FIR Compiler II MegaCore Function User Manual

Page 45: Vectorized inputs -12

To achieve TDM, the IP core requires a serializer and deserializer before and after the reused hardware

block to control the timing. The ratio of system clock frequency to sample rate determines the amount of

resource saving except for a small amount of additional logic for the serializer and deserializer.

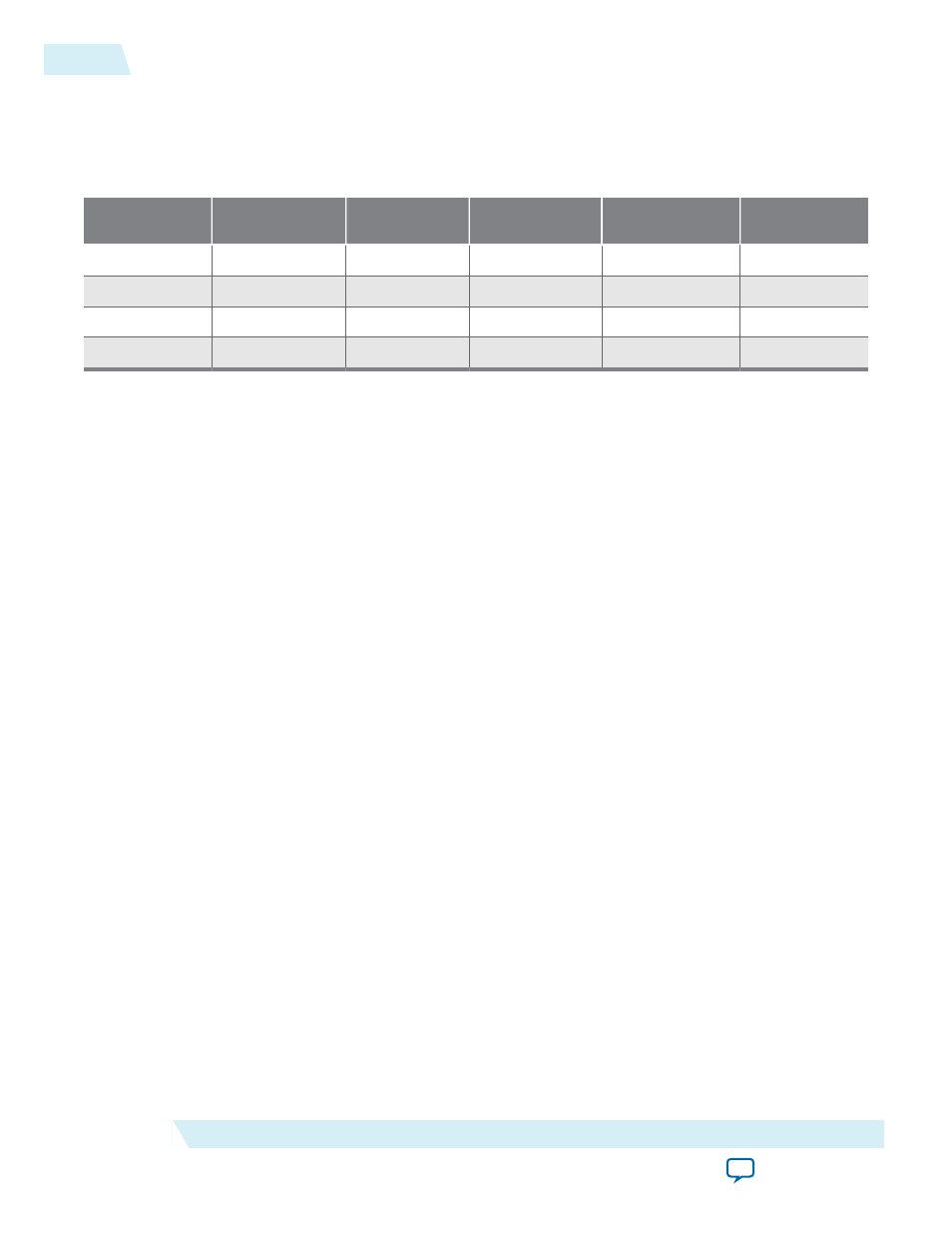

Table 4-2: Estimated Resources Required for a 49-Tap Single Rate Symmetric FIR II IP core Filter

Clock Rate

(MHz)

Sample Rate

(MSPS)

Logic

Multipliers

Memory Bits

TDM Factor

72

72

2230

25

0

1

144

72

1701

13

468

2

288

72

1145

7

504

4

72

36

1701

13

468

2

When the sample rate equals the clock rate, the filter is symmetric and you only need 25 multipliers.

When you increase the clock rate to twice the sample rate, the number of multipliers drops to 13. When

the clock rate is set to 4 times the sample rate, the number of multipliers drops to 7. If the clock rate stays

the same while the new data sample rate is only 36 MSPS (million samples per second), the resource

consumption is the same as twice the sample rate case.

FIR II IP Core Multichannel Operation

You can build multichannel systems directly using the required channel count, rather than creating a

single channel system and scaling it up. The IP core uses vectors of wires to scale without having to cut

and paste multiple blocks.

You can vectorize the FIR II IP core. If data going into the block is a vector requiring multiple instances of

a FIR filter, teh IP core creates multiple FIR blocks in parallel behind a single FIR II IP core block. If a

decimating filter requires a smaller vector on the output, the data from individual filters is automatically

time-division multiplexed onto the output vector. This feature relieves the necessity of gluing filters

together with custom logic.

Vectorized Inputs

The data inputs and outputs for the FIR II IP core blocks can be vectors. Use this capability when the

clock rate is insufficiently high to carry the total aggregate data. For example, 10 channels at 20 MSPS

require 10 × 20 = 200 MSPS aggregate data rate. If you set the system clock rate to 100 MHz, two wires are

required to carry this data, and so the FIR II IP core uses a vector of width 2.

This approach is unlike traditional methods because you do not need to manually instantiate two FIR

filters and pass a single wire to each in parallel. Each FIR II IP core block internally vectorizes itself. For

example, a FIR II IP core block can build two FIR filters in parallel and wire one element of the vector up

to each FIR. The same paradigm is used on outputs, where high data rates on multiple wires are

represented as vectors.

The input and output wire counts are determined by each FIR II IP core based on the clock rate, sample

rate, and number of channels.

The output wire count is also affected by any rate changes in the FIR II IP core. If there is a rate change,

such interpolating by two, the output aggregate sample rate doubles. The output channels are then packed

4-12

FIR II IP Core Multichannel Operation

UG-01072

2014.12.15

Altera Corporation

FIR II IP Core Functional Description