Using cdelay ram block threshold, Using cdual mem dist ram threshold, Using cdelay ram block threshold -7 – Altera FIR Compiler II MegaCore Function User Manual

Page 32: Using cdual mem dist ram threshold -7

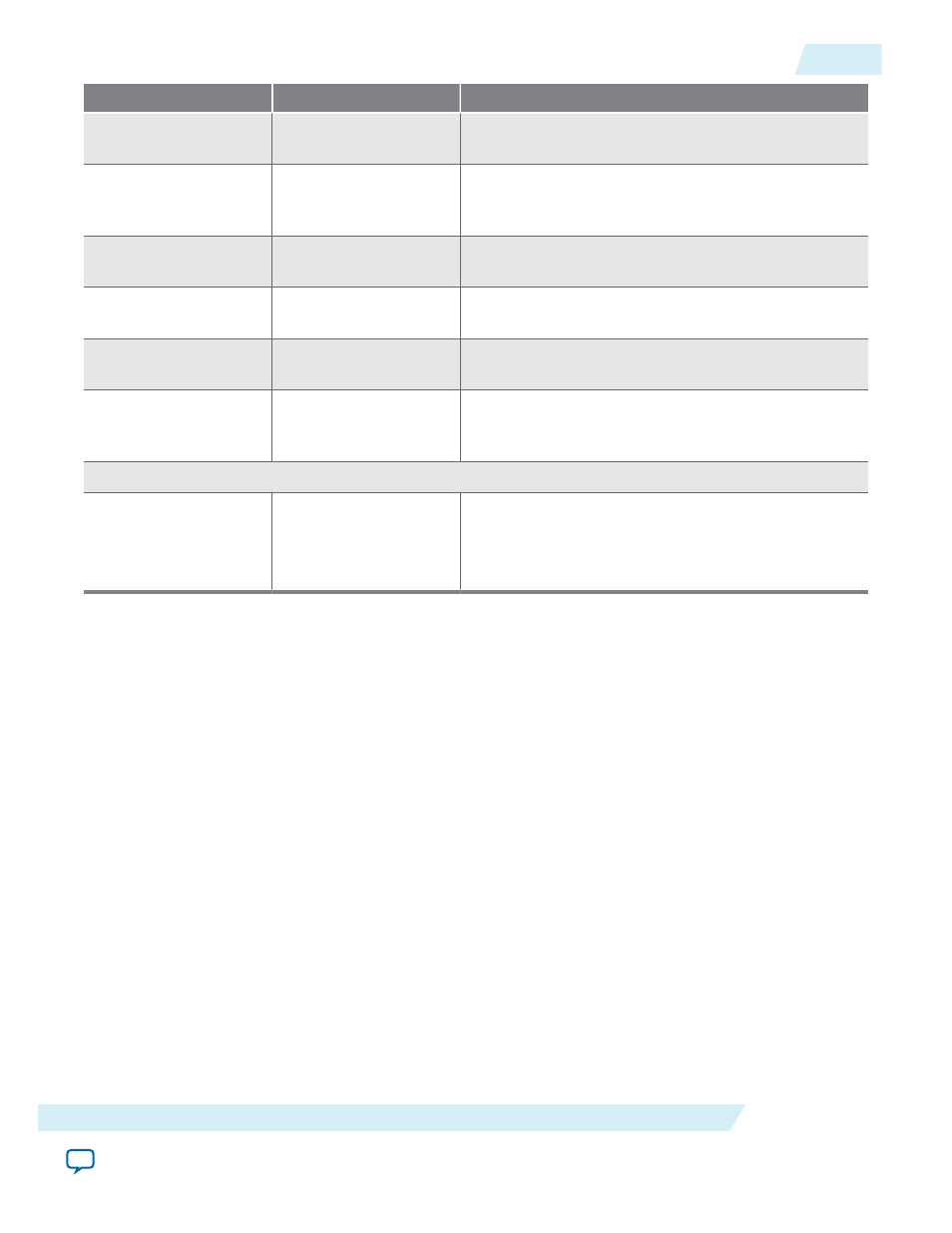

Parameter

Value

Description

Device Family

Menu of supported

devices

Specifies the target device family.

Speed grade

Fast, medium, slow

Specifies the speed grade of the target device to

balance the size of the hardware against the resources

required to meet the clock frequency.

CDelay RAM Block

Threshold

Integer

Specifies the balance of resources between LEs/Small

RAM block threshold in bits.

CDual Mem Dist

RAM Threshold

Integer

Specifies the balance of resources between small to

medium RAM block threshold in bits.

M-RAM Threshold

Integer

Specifies the balance of resources between medium to

large RAM block threshold in bits.

Hard Multiplier

Threshold

Integer

Specifies the balance of resources between LEs/ DSP

block multiplier threshold in bits. The default value is

-1.

Symmetry Option

Symmetry Mode

Non Symmetry

Symmetrical

Anti-Symmetrical

Specifies whether your filter design uses non-

symmetric, symmetric, or anti-symmetric coefficients.

The default value is Non Symmetry.

These topics describe the memory and multiplier threshold trade-offs, and provide some usage examples.

Using CDelay RAM Block Threshold

This threshold is the trade-off between simple delay LEs and small ROM blocks. If any delay’s size is such

that the number of LEs is greater than this parameter, the IP core implements delay as block RAM.

1. To make more delays using block RAM, enter a lower number, such as a value in the range of 20–30.

2. To use fewer block memories, enter a larger number, such as 100.

3. To never use block memory for simple delays, enter a very large number, such as 10000.

4. Implement delays of less than three cycles in LEs because of block RAM behavior.

Note: This threshold only applies to implementing simple delays in memory blocks or logic elements.

You cannot push dual memories back into logic elements.

Using CDual Mem Dist RAM Threshold

This threshold is trade-off between small and medium RAM blocks. This threshold is similar to the Using

LEs / Small RAM Block Threshold except that it applies only to the dual-port memories.

The IP core implements any dual-port memory in a block memory rather than logic elements, but for

some device families different sizes of block memory may be available. The threshold value determines

which medium-size RAM memory blocks IP core implements instead of small-memory RAM blocks. For

UG-01072

2014.12.15

Using CDelay RAM Block Threshold

3-7

FIR II IP Core Parameters

Altera Corporation