Channelization, Channelization -13 – Altera FIR Compiler II MegaCore Function User Manual

Page 46

into the fewest number of wires (vector width) that will support that rate. For example, an interpolate by

two FIR II IP core filters might have two wires at the input, but three wires at the output.

Any necessary multiplexing and packing is performed by the FIR II IP core. The blocks connected to the

inputs and outputs must have the same vector widths. Vector width errors can usually be resolved by

carefully changing the sample rates.

Channelization

The number of wires and the number of channels carried on each wire are determined by

parameterization, which you can specify using the following variables:

• clockRate is the system clock frequency (MHz).

• inputRate is the data sample rate per channel (MSPS).

• inputChannelNum is the number of channels. Channels are enumerated from 0 to inputChan‐

nelNum–1.

• The period (or TDM factor) is the ratio of the clock rate to the sample rate and determines the number

of available time slots.

• ChanWireCount is the number of channel wires required to carry all the channels. It can be calculated

by dividing the number of channels by the TDM factor. More specifically:

• PhysChanIn = Number of channel input wires

• PhysChanOut = Number of channel output wires

• ChanCycleCount is the number of channels carried per wire. It is calculated by dividing the number of

channels by the number of channels per wire. The channel signal counts from 0 to ChanCycleCount–

1. More specifically:

• ChansPerPhyIn = Number of channels per input wire

• ChansPerPhyOut = Number of channels per output wire

If the number of channels is greater than the clock period, multiple wires are required. Each FIR II IP core

in your design is internally vectorized to build multiple FIR filters in parallel.

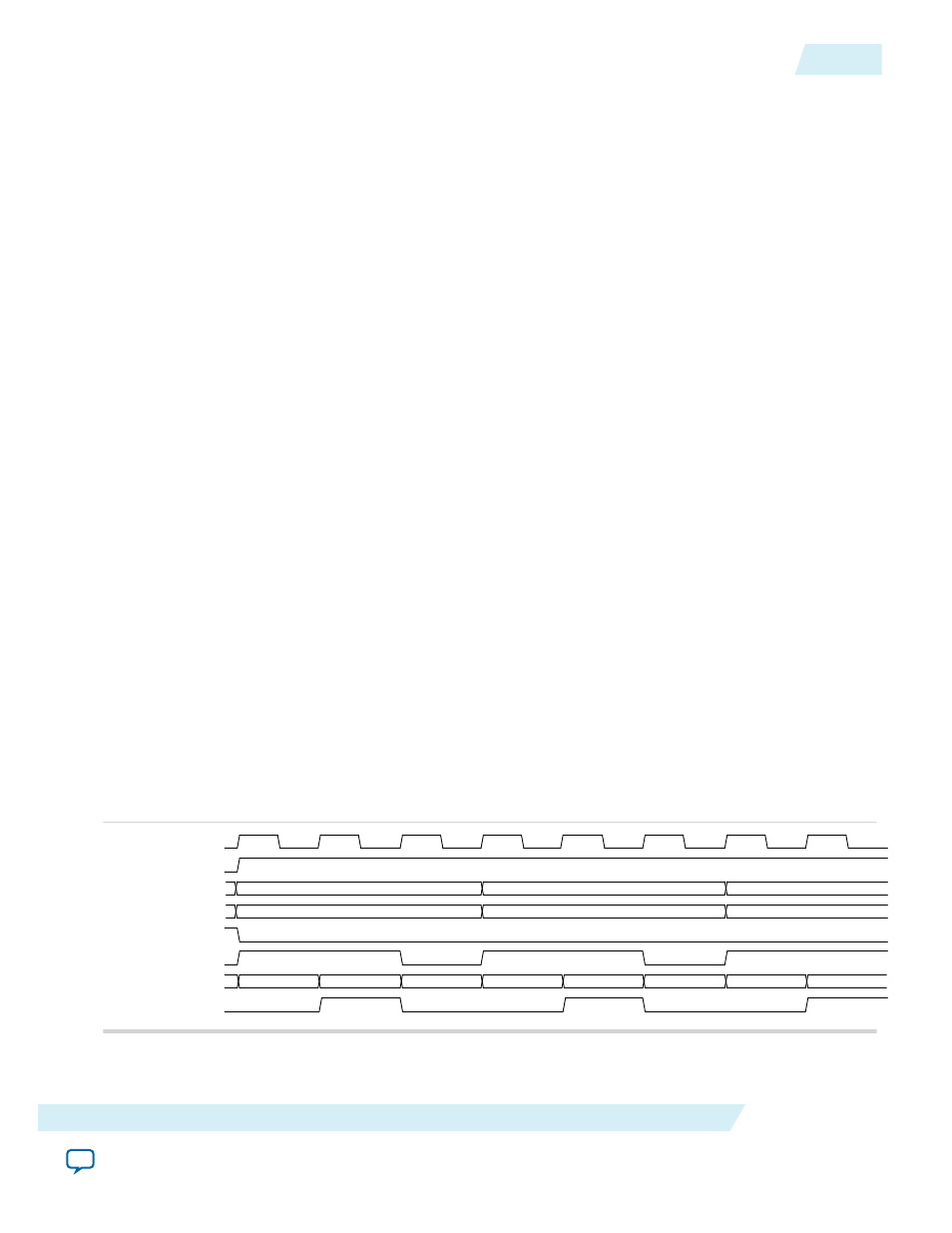

Figure 4-9: Channelization of Two Channels with a TDM Factor of 3

A TDM factor of 3 combines two input channels into a single output wire. (inputChannelNum = 2,

ChanWireCount = 1, ChanCycleCount = 2). This example has three available time slots in the output

channel and every third time slot has a ‘don't care’ value when the valid signal is low. The value of the

channel signal while the valid signal is low does not matter.

clock

input_valid

input_data_channel_0

input_data_channel_1

input_channel

output_valid

TDM_output_data

output_channel

c0(0)

c0(1)

c0(2)

c1(0)

c1(1)

c1(2)

c0(0)

c1(0)

don’t care

c0(1)

c1(1)

don’t care

c0(2)

c1(2)

UG-01072

2014.12.15

Channelization

4-13

FIR II IP Core Functional Description

Altera Corporation