Altera 50G Interlaken MegaCore Function User Manual

Page 52

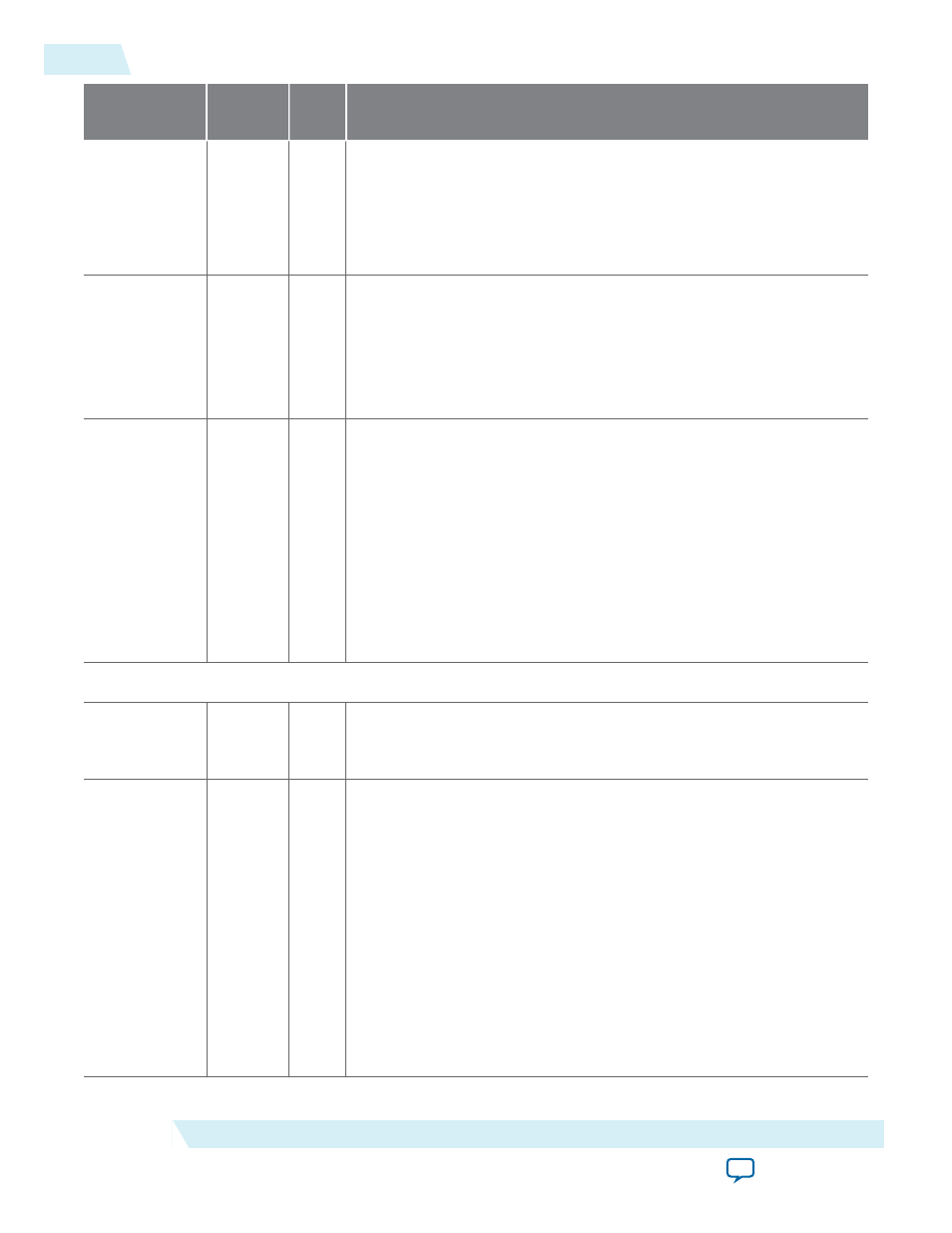

Signal Name

Direction Width

(Bits)

Description

itx_

calendar

Input

16 N

Multiple pages (16 bits per page) of calendar input bits. The

50G Interlaken IP Core copies these bits to the in-band flow control

bits in N control words that it sends on the Interlaken link. N is the

value of the Number of calendar pages parameter, which can be any of

1, 2, 4, 8. or 16. This signal is synchronous with

tx_usr_clk

, although

it is not part of the user data transfer protocol.

itx_ready

Output

1

Flow control signal to back pressure transmit traffic. When this signal

is high, you can send traffic to the IP core. When this signal is low, you

should stop sending traffic to the IP core within one to four cycles.

You can consider the inverse of

itx_ready

to be a FIFO-almost-full

indicator. In full duplex mode,

itx_ready

is low when

rx_lanes_

aligned

is low.

itx_ifc_

err

Output

1

Indicates the transmit side user data transfer interface received traffic

that the 50G Interlaken IP Core does not support. The IP core asserts

the

itx_ifc_err

signal in the following cases:

• In Interleaved mode, the IP core receives a burst that exceeds the

size of MaxBurst.

• Two instances of non-zero

itx_sop

(a start of packet), or two

instances of non-zero

itx_sob

(a start of burst), are separated by

fewer than 64 bytes.

The IP core asserts the

itx_ifc_err

signal for a single clock cycle. The

signal pulses within the current burst, with a delay of one or two cycles

after the error on the transmit side user data transfer interface.

50G Interlaken IP Core Receive User Interface

irx_chan

Output

8

Receive logic channel number. The IP core supports up to 256

channels. You should sample this value when

irx_sop

or

irx_sob

is

high and

irx_num_valid

has a non-zero value.

irx_num_

valid

Output

3

irx_num_valid[2:0]

specifies the number of valid 64-bit words in the

current packet in the current data symbol. The maximum value of

irx_num_valid[2:0]

is four, because a data symbol on the 256 bit

wide data path has four words (4 x 64 bits = 256 bits).

In valid cycles, the IP core sets the value of

irx_num_valid[2:0]

as

follows:

• 3’b100: if all four words contain valid data from the current packet.

• 3’b0xx: where xx indicates the number of valid words that are part

of the current packet, if the number is less than four. Data is always

MSB aligned (left aligned). For example, the value of 3’b011

indicates that word 0 (bit [63:0]) is not valid.

The IP core sets the value of

irx_num_valid

to zero in all non-valid

cycles.

5-6

50G Interlaken IP Core User Data Transfer Interface Signals

UG-01140

2015.05.04

Altera Corporation

50G Interlaken MegaCore Function Signals