4 end-limit signals pel and mel, End-limit signals pel and mel – ADLINK PCI-8154 User Manual

Page 37

Signal Connections

27

3.4

End-Limit Signals PEL and MEL

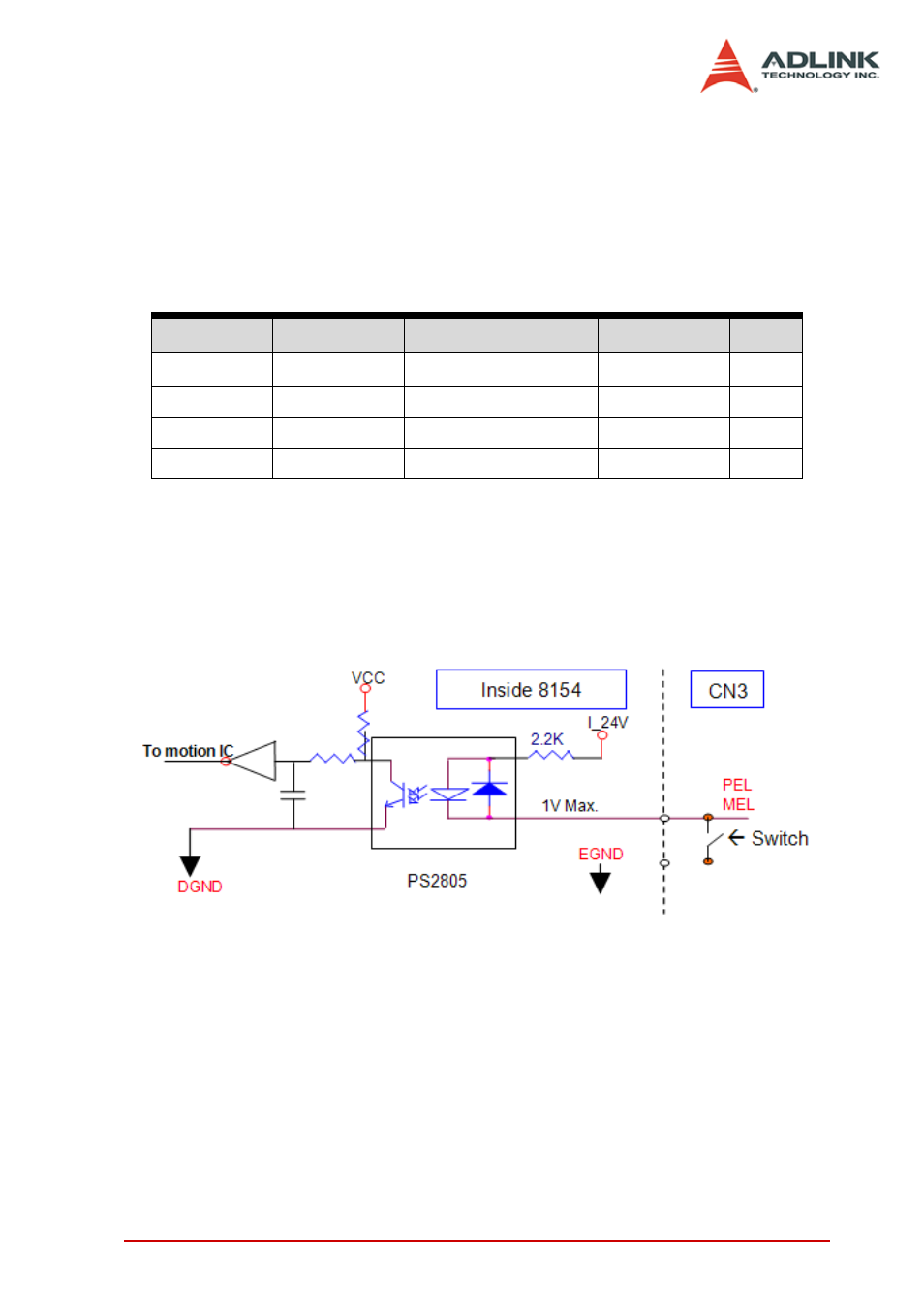

There are two end-limit signals PEL and MEL for each axis. PEL

indicates the end limit signal is in the plus direction and MEL indi-

cates the end limit signal is in the minus direction. The signal

names, pin numbers, and axis numbers are shown in the table

below:

A circuit diagram is shown in the diagram below. The external limit

switch should have a contact capacity of +24V @ 8mA minimum.

Either ‘A-type’ (normal open) contact or ‘B-type’ (normal closed)

contact switches can be used. To set the active logic of the exter-

nal limit signal, please refer to the explanation of

_8154_set_limit_logic function.

CN3 Pin No Signal Name Axis # CN3 Pin No Signal Name Axis #

37

PEL0

0

38

MEL0

0

43

PEL1

1

44

MEL1

1

87

PEL2

2

88

MEL2

2

93

PEL3

3

94

MEL3

3

- USB-1901 (84 pages)

- USB-1210 (54 pages)

- USB-2401 (60 pages)

- USB-7230 (50 pages)

- USB-2405 (56 pages)

- DAQe-2010 (92 pages)

- DAQe-2204 (100 pages)

- DAQe-2213 (94 pages)

- DAQe-2501 (74 pages)

- PXI-2010 (84 pages)

- PXI-2020 (60 pages)

- PXI-2501 (62 pages)

- cPCI-9116 (98 pages)

- ACL-8112 Series (93 pages)

- ACL-8112 Series (94 pages)

- ACL-8112 Series (92 pages)

- ACL-8216 (75 pages)

- ACL-8111 (61 pages)

- PCM-9112+ (94 pages)

- PCM-9112+ (10 pages)

- cPCI-6216V (47 pages)

- ACL-6126 (28 pages)

- ACL-6128A (40 pages)

- PCM-6308V+ (52 pages)

- PCM-6308V+ (4 pages)

- PCI-7444 (82 pages)

- PCI-7434 (48 pages)

- PCI-7234 (56 pages)

- PCI-7260 (66 pages)

- PCI-7258 (38 pages)

- PCI-7256 (48 pages)

- PCI-7250 (48 pages)

- LPCI-7250 (48 pages)

- PCI-7396 (65 pages)

- PCI-7296 (59 pages)

- PCI-8554 (67 pages)

- PCIe-7360 (94 pages)

- PCIe-7350 (86 pages)

- PCIe-7300A (114 pages)

- PCIe-7200 (51 pages)

- PCI-7300A (112 pages)

- PCI-7300A (83 pages)

- PCI-7200 (96 pages)

- cPCI-7300 (83 pages)

- cPCI-7300 (82 pages)