Table 3-59: 0x339: cpu control register, Table 3-60: 0x33a: board variant register, Table 3-61: 0x350: pcie status register – Kontron COMe-cP2020 User Manual

Page 66: Table 3-59, Table 3-60, Table 3-61

www.kontron.com

COMe-P2020 User Guide

66

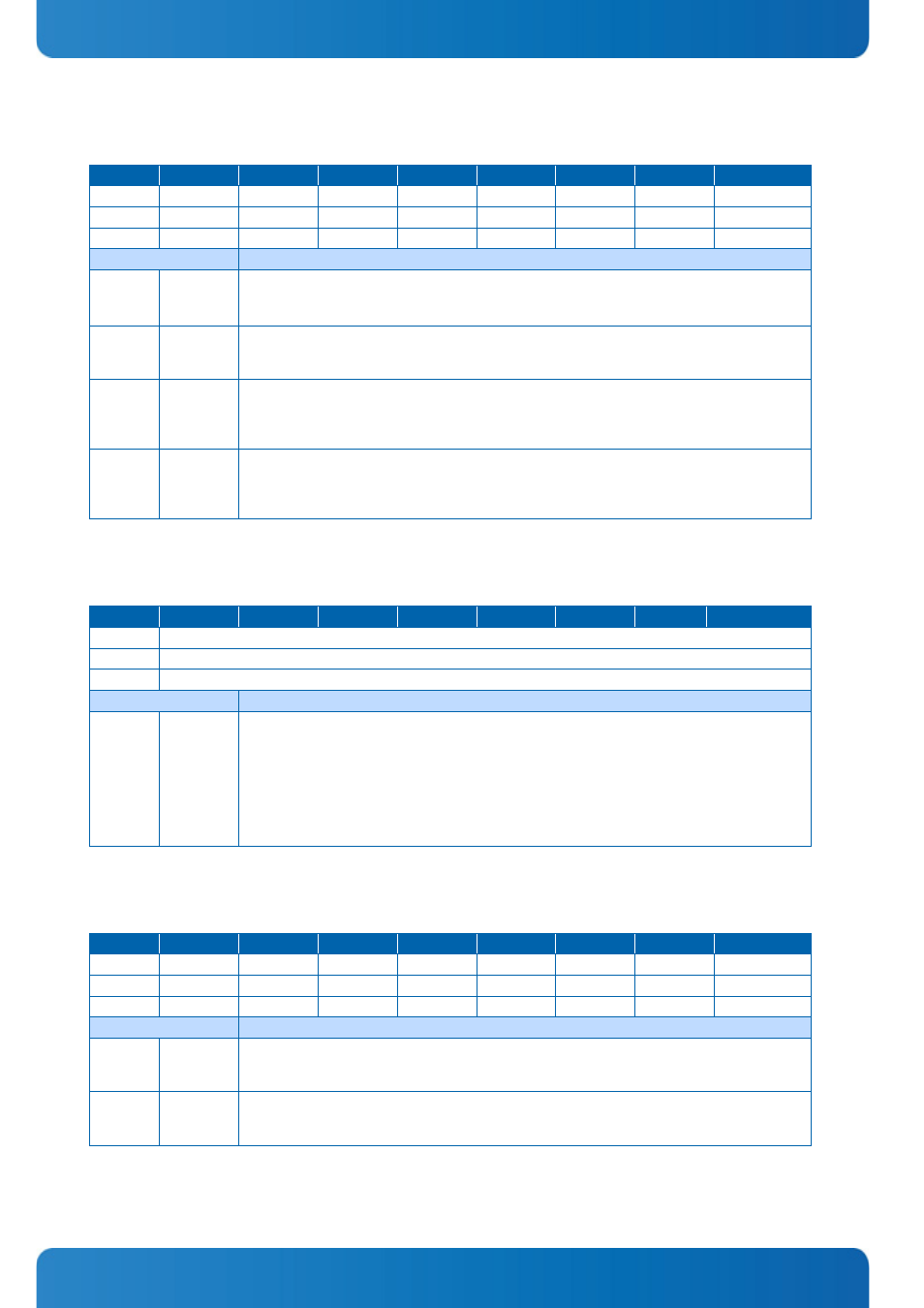

Table 3-59:

0x339: CPU Control Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

0

0

0

0

0

0

0

0

WRITE

NU

NU

NU

NU

CCntrl3

CCntrl2

CCntrl1

CCntrl0

POWER UP

0

0

0

0

0

0

0

0

BITFIELD

DESCRIPTION

[D0]

CCntrl0

Core#0 unconditional Debug request:

'0' = no request

'1' = Debug request is triggered (bit is set by CPU and self cleared by CPLD, length is about 1us)

[D1]

CCntrl1

Core#1 unconditional Debug request:

'0' = no request

'1' = Debug request is triggered (bit is set by CPU and self cleared by CPLD, length is about 1us)

[D2]

CCntrl2

Core#0 Machine check request:

'0' = no request

'1' = Machine check request is triggered (bit is set by CPU and self cleared by CPLD, length is

about 1us)

[D3]

CCntrl3

Core#1 Machine check request:

'0' = no request

'1' = Machine check request is triggered (bit is set by CPU and self cleared by CPLD, length is

about 1us)

Table 3-60:

0x33A: Board Variant Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

BrdVar

WRITE

BrdVar

POWER UP

0xXX

BITFIELD

DESCRIPTION

[D0-D7]

BrdVar

Register shows current Board Variant depends on strapping option:

Board Variant: => Strapping:

P2020/1200MHz/667MHz => 0xE0

P2020/1000MHz/667MHz => 0xD0

P2020/1200MHz/800MHz => 0xE8

P2010/1200MHz/800MHz => 0xA8

P1020/800MHz/667MHz => 0x40

Table 3-61:

0x350: PCIe Status Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

0

0

0

0

0

0

CPPE1

CPPE0

WRITE

NU

NU

NU

NU

NU

NU

CPPE1

CPPE0

POWER UP

0

0

0

0

0

0

0

0

BITFIELD

DESCRIPTION

[D0]

CPPE0

PCIe slot#0 card request:

'0' = Card is not present

'1' = Card is present

[D1]

CPPE1

PCIe slot#1 card request:

'0' = Card is not present

'1' = Card is present