Table 3-18: 0x00e: user core1 speed register, Table 3-18, Table 3-19 – Kontron COMe-cP2020 User Manual

Page 50

www.kontron.com

COMe-P2020 User Guide

50

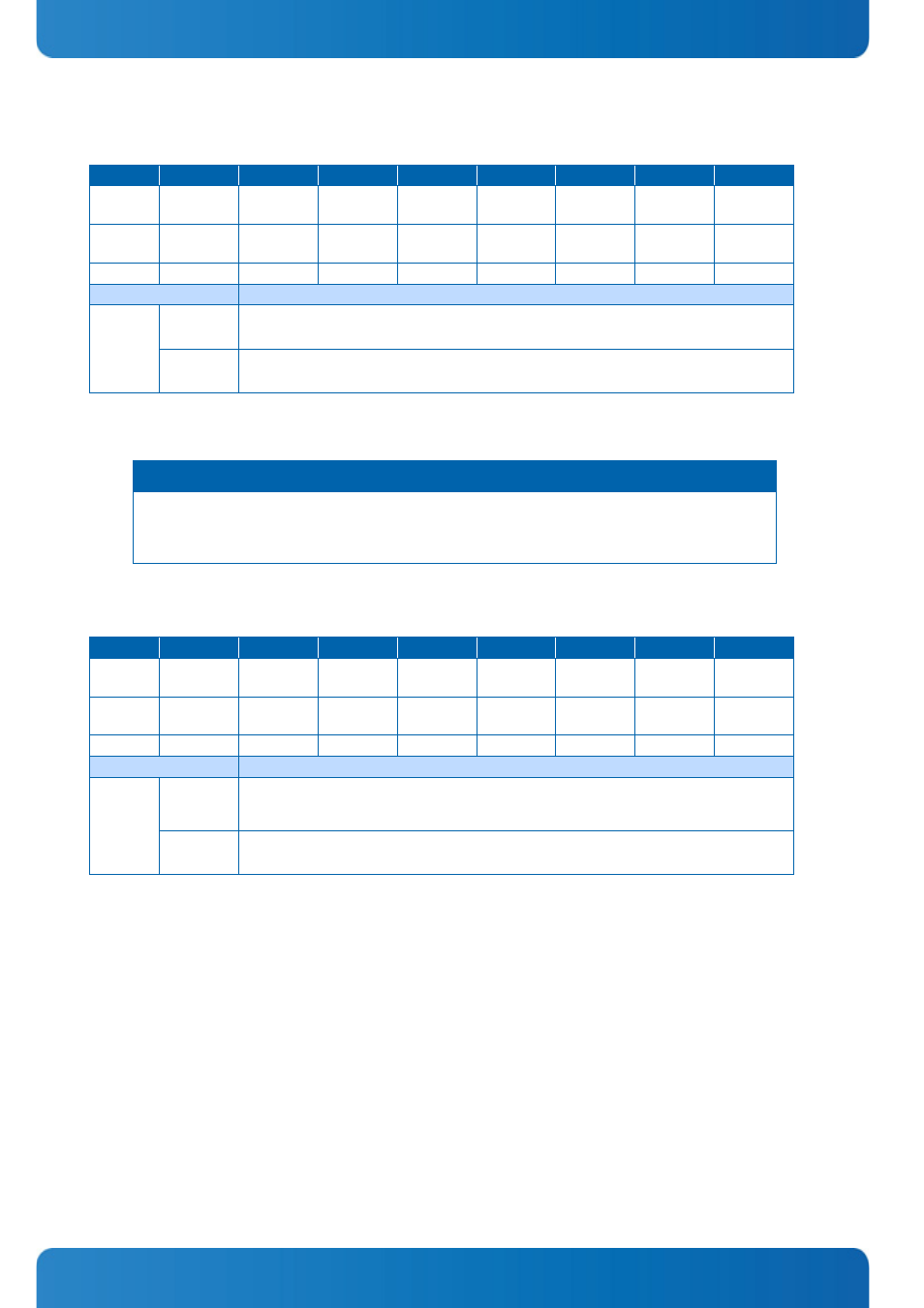

Table 3-18:

0x00E: User Core1 Speed Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

NU

cfg_core1_sp

eed

WRITE

NU

NU

NU

NU

NU

NU

NU

cfg_core1_sp

eed

POWER UP

1

1

1

1

1

1

1

1

BITFIELD

DESCRIPTION

[D0]

00

Core 1 clock frequency is less than or equal to 1000 MHz.

01

Core 1 clock frequency is greater than 1000 MHz.

N O T I C E

Register value is no more used to force CPU strapping, but register is used for checksum calculation!

(write Register value to 0x00). Equivalent CPU strapping is hard coded in CPLD depends on board vari-

ant!

Table 3-19:

0x00F: User SerDes OLL Time-out Enable Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

NU

cfg_srds_pll

_toe

WRITE

NU

NU

NU

NU

NU

NU

NU

cfg_srds_pll

_toe

POWER UP

1

1

1

1

1

1

1

1

BITFIELD

DESCRIPTION

[D0]

00

Enable PLL lock time-out counter. The power-on-reset sequence

waits for the SerDes PLL to lock while the time-out counter has not

expired.

01

Disable PLL lock time-out counter. The power-on-reset sequence

waits indefinately for the SerDes PLL to lock.