Table 3-7: 0x003: user boot configuration register, Table 3-7, Table 3-8 – Kontron COMe-cP2020 User Manual

Page 46: Table 3-9

www.kontron.com

COMe-P2020 User Guide

46

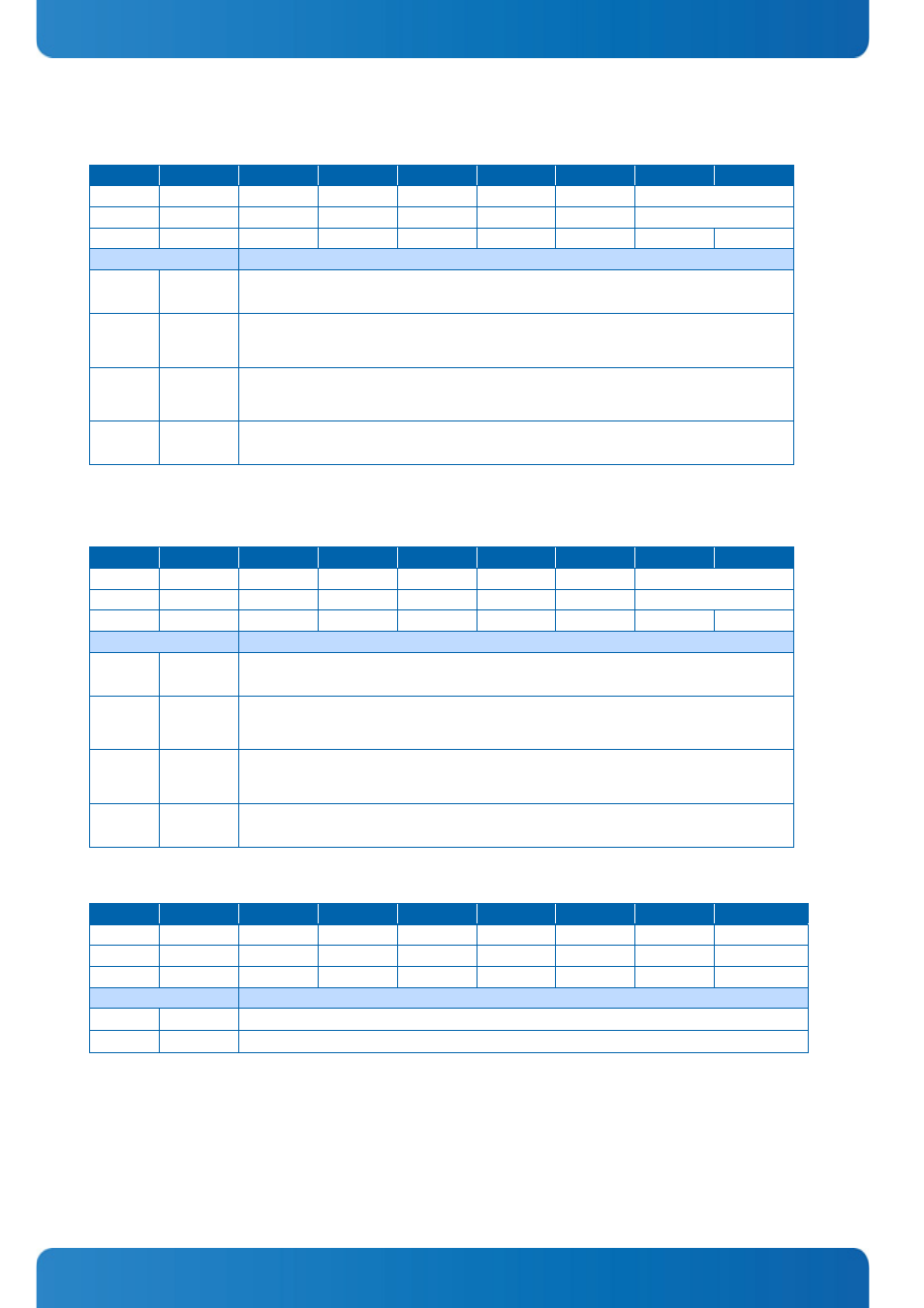

Table 3-7:

0x003: User Boot Configuration Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

cfg_cpu0/1_boot

WRITE

NU

NU

NU

NU

NU

NU

cfg_cpu0/1_boot

POWER UP

1

1

1

1

1

1

1

1

BITFIELD

DESCRIPTION

[D1-D0]

00

CPU boot holdoff mode for both cores. The e500 cores are prevented

from booting until conf igured by an external master.

01

e500 core 1 is allowed to boot without waiting for conf iguration by an

external master, while e500 core 0 is prevented from booting until

configured by an external master or the other core.

10

e500 core 0 is allowed to boot without waiting for conf iguration by an

external master, while e500 core 1 is prevented from booting until

configured by an external master or the other core.

11

Both e500 cores are allowed to boot without waiting for configuration by

an external master.

Table 3-8:

0x004: User Boot Sequencer Configuration Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

cfg_boot_seq[0:1]

WRITE

NU

NU

NU

NU

NU

NU

cfg_boot_seq[0:1]

POWER UP

1

1

1

1

1

1

1

1

BITFIELD

DESCRIPTION

[D1-D0]

00

Reserved

01

Normal I2C addressing mode is used. Boot sequencer is enabled and

loads configuration information from a ROM on the I2C1 interface. A

valid ROM must be present.

10

Extended I2C addressing mode is used. Boot sequencer is enabled

and loads configuration information from a ROM on the I2C1 interface.

A valid ROM must be present.

11

Boot sequencer is disabled. No I2C ROM is accessed.

Table 3-9:

0x005: User SerDes Reference Clock Configuration Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

NU

cfg_srds_refclk

WRITE

NU

NU

NU

NU

NU

NU

NU

cfg_srds_refclk

POWER UP

1

1

1

1

1

1

1

1

BITFIELD

DESCRIPTION

[D0]

0

SerDes expects a 125 MHz reference clock frequency.

1

SerDes expects a 100 MHz reference clock frequency.