Table 3-13, Table 3-14 – Kontron COMe-cP2020 User Manual

Page 48

www.kontron.com

COMe-P2020 User Guide

48

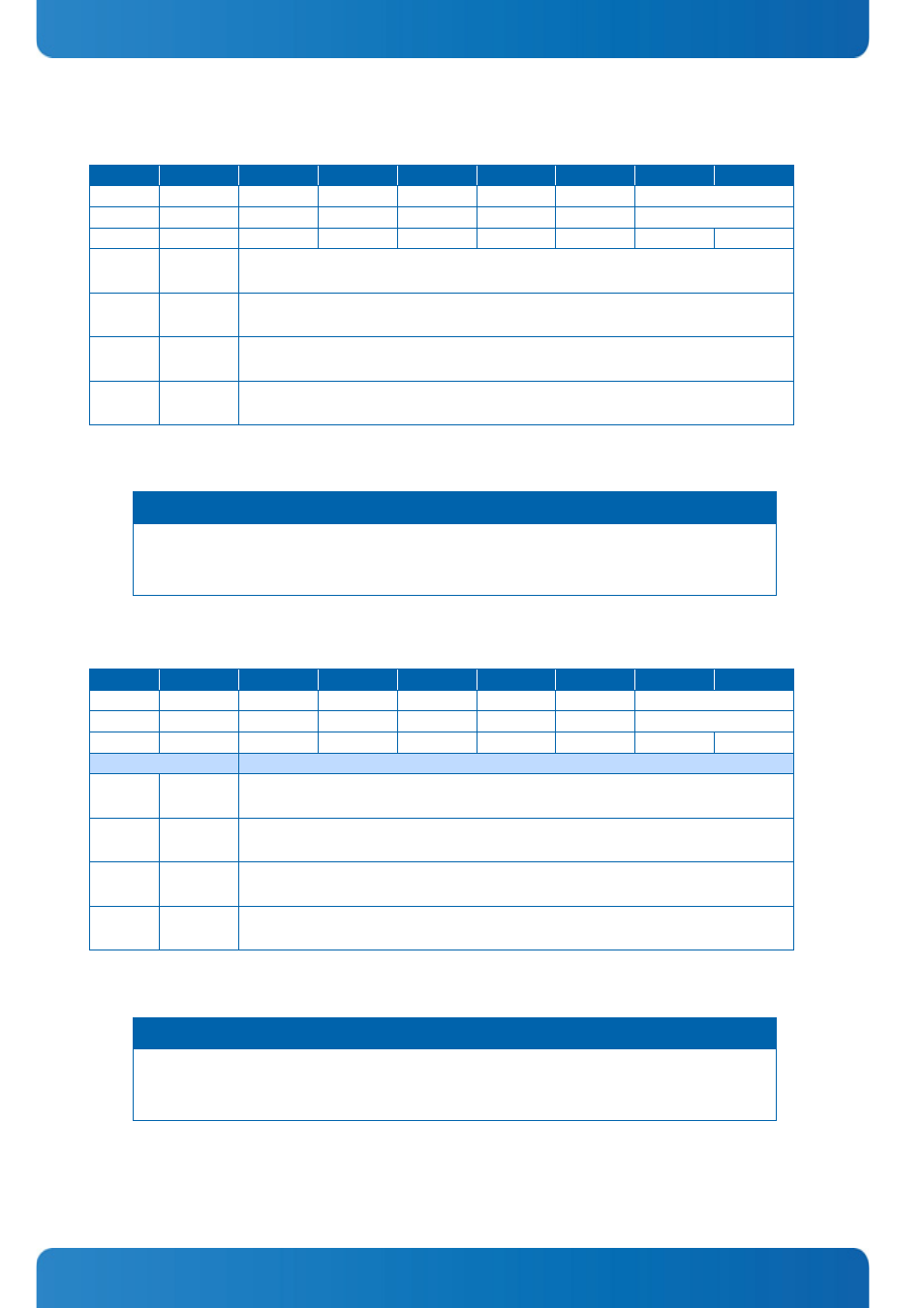

Table 3-13:

0x009: User eTSEC2 Protocol Configuration Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

cfg_tsec2_prto[0:1]

WRITE

NU

NU

NU

NU

NU

NU

cfg_tsec2_prto[0:1]

POWER UP

1

1

1

1

1

1

1

1

[D1-D0]

00

Reserved

01

The eTSEC2 controller operates using the MII protocol (or RMII if

configured in reduced mode if not conf igured to operate in SGMII mode.

10

The eTSEC2 controller operates using the GMII protocol (or RGMII if

configured in reduced mode if not conf igured to operate in SGMII mode.

11

The eTSEC2 controller operates using the TBI protocol (or RTBI if

configured in reduced mode if not conf igured to operate in SGMII mode.

N O T I C E

Register value is no more used to force CPU strapping, but register is used for checksum calculation!

(write Register value to 0x00). Equivalent CPU strapping is hard coded in CPLD depends on board vari-

ant, value is 10b.

Table 3-14:

0x00A: User eTSEC3 Protocol Configuration Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

cfg_tsec2_prto[0:1]

WRITE

NU

NU

NU

NU

NU

NU

cfg_tsec2_prto[0:1]

POWER UP

1

1

1

1

1

1

1

1

BITFIELD

DESCRIPTION

[D1-D0]

00

Reserved

01

The eTSEC3 controller operates using the RMII protocol if not configured

to operate in SGMII mode.

10

The eTSEC3 controller operates using the RGMII protocol if not

configured to operate in SGMII mode.

11

The eTSEC3 controller operates using the RTBI protocol if not conf igured

to operate in SGMII mode (default).

N O T I C E

Register value is no more used to force CPU strapping, but register is used for checksum calculation!

(write Register value to 0x00). Equivalent CPU strapping is hard coded in CPLD depends on board vari-

ant, value is 10b.