Table 2-7: serdes protocol mapping – Kontron COMe-cP2020 User Manual

Page 34

www.kontron.com

COMe-P2020 User Guide

34

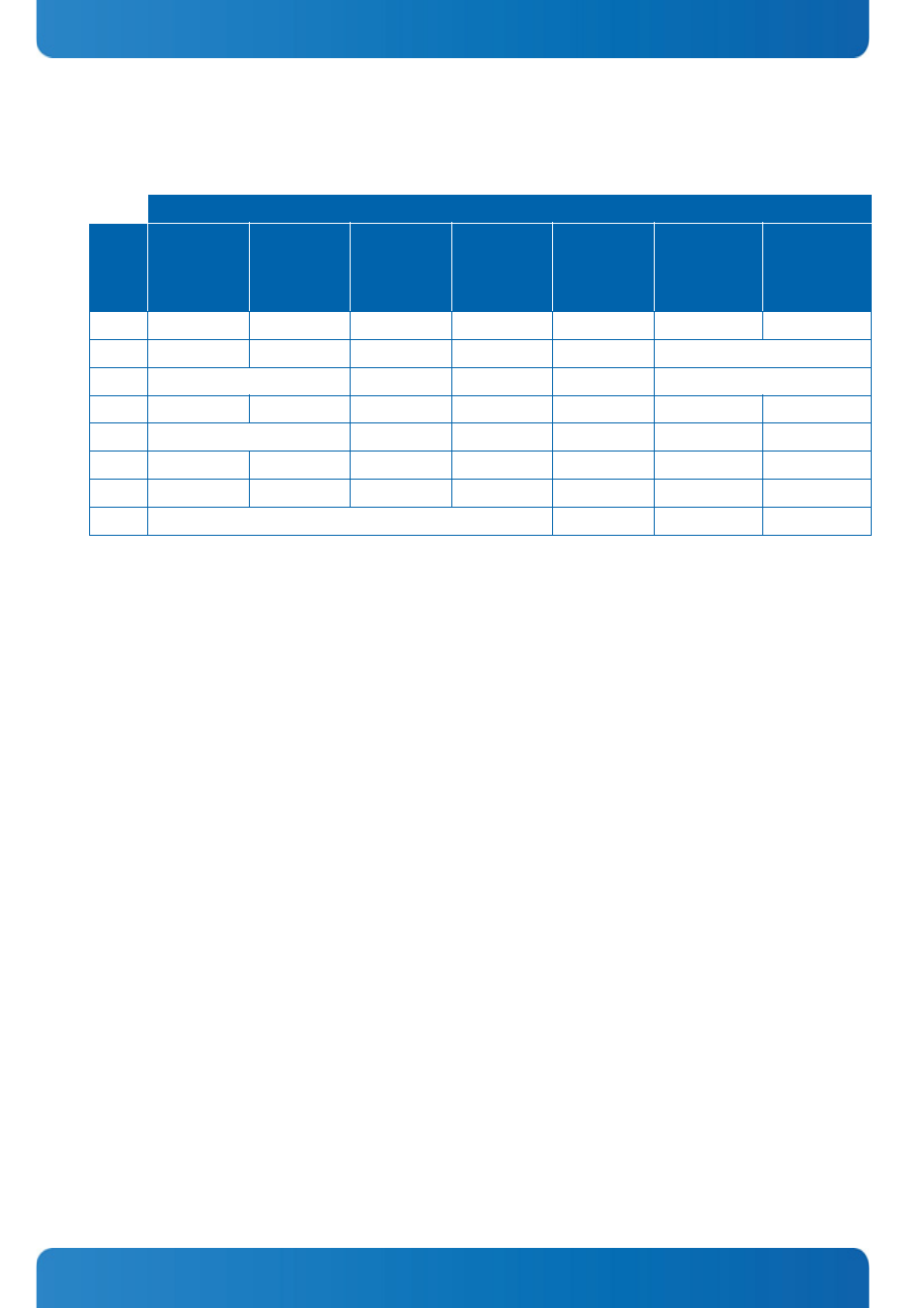

The following SerDes protocol combinations can be selected by using the “sconf” command:

2.5.2.5

Local Bus / GPIO

2.5.2.5.1

Local Bus

The COMe-cP2020 provides a local bus interface for connecting directly memory mapped parallel bus devices (SRAM-style).

The Local Bus implementation on the COMe-cP2020 supports 8-bit and 16-bit data signal paths depending on the Local Bus

chip select configuration and an 8Mbyte address range for each of the two Local Bus chip selects.

The Local Bus signals designated as LAD0..15 incorporate multipexed address and data information, whereby the Local Bus

signals LA16..31 are dedicated address lines. Please be aware that external address latches must be provided on the

LAD8..15 lines if an address range greater than 64kB is to be addressed.

The numbering scheme for the Local Bus LA/LAD pins is noted in Power Architecture style, meaning that LAD0 is the most

significant bit and LA31 is the least significant bit.

For a better understanding of the QorIQ P2020 Local Bus functionality and all the involved control signals please refer to

the CPU’s reference manual.

2.5.2.5.2

GPIO

The COMe-cP2020 provides the possibility to convert part of the Interrupt signals to GPIO functionality. There are 5 signals

on the COM Express connector which can be multiplexed between Interrupt functionality and GPIO functionality.

2.5.2.6

USB

The COMe-cP2020 supports four USB 2.0 high speed USB ports.

The USB ports USB0..3 at the COM Express connectors are provided using a 4-port USB hub with its Uplink-Port connected

via an external USB-PHY to the USB controller ULPIO-Interface on the QorIQ P2020.

2.5.2.7

SDHC (SDIO)

The Freescale QorIQ CPUs incorporate an enhanced Secure Digital Host Controller (eSDHC) which provides support for Mul-

tiMediaCards (MMC) and Secure Digital (SD) Cards.

The interfacing signals of the CPU are multiplexed between the on-board SD card socket and the dedicated SDIO signals on

the COM Express connectors. The selection between on-board socket and external interfacing is done via the DIP Switch

SW1, switch 1.

Table 2-7:

SerDes Protocol Mapping

COMe-CONNECTOR

BASE

CON-

FIG.

SERDES_

TX/RX[0]+/-

SERDES_

TX/RX[1]+/-

SERDES_

TX/RX[2]+/-

SERDES_

TX/RX[3]+/-

SERDES_

TX/RX[4]+/-

SERDES_

TX/RX[10]+/-

SERDES_

TX/RX[11]+/-

1

off

off

off

off

off

off

off

2

PCIex1

off

off

off

PCIex1

PCIex2

3

PCIex2

off

off

off

PCIex2

4

PCIex1

off

off

off

PCIex1

SGMII

SGMII

5

PCIex2

off

off

off

SGMII

SGMII

6

PCIex1

off

off

off

SRIOx1

SGMII

SGMII

7

SRIOx1

off

off

off

SRIOx1

SGMII

SGMII

8

SRIOx4

off

off

off