Table 3-53, Table 3-54, Table 3-55 – Kontron COMe-cP2020 User Manual

Page 64

www.kontron.com

COMe-P2020 User Guide

64

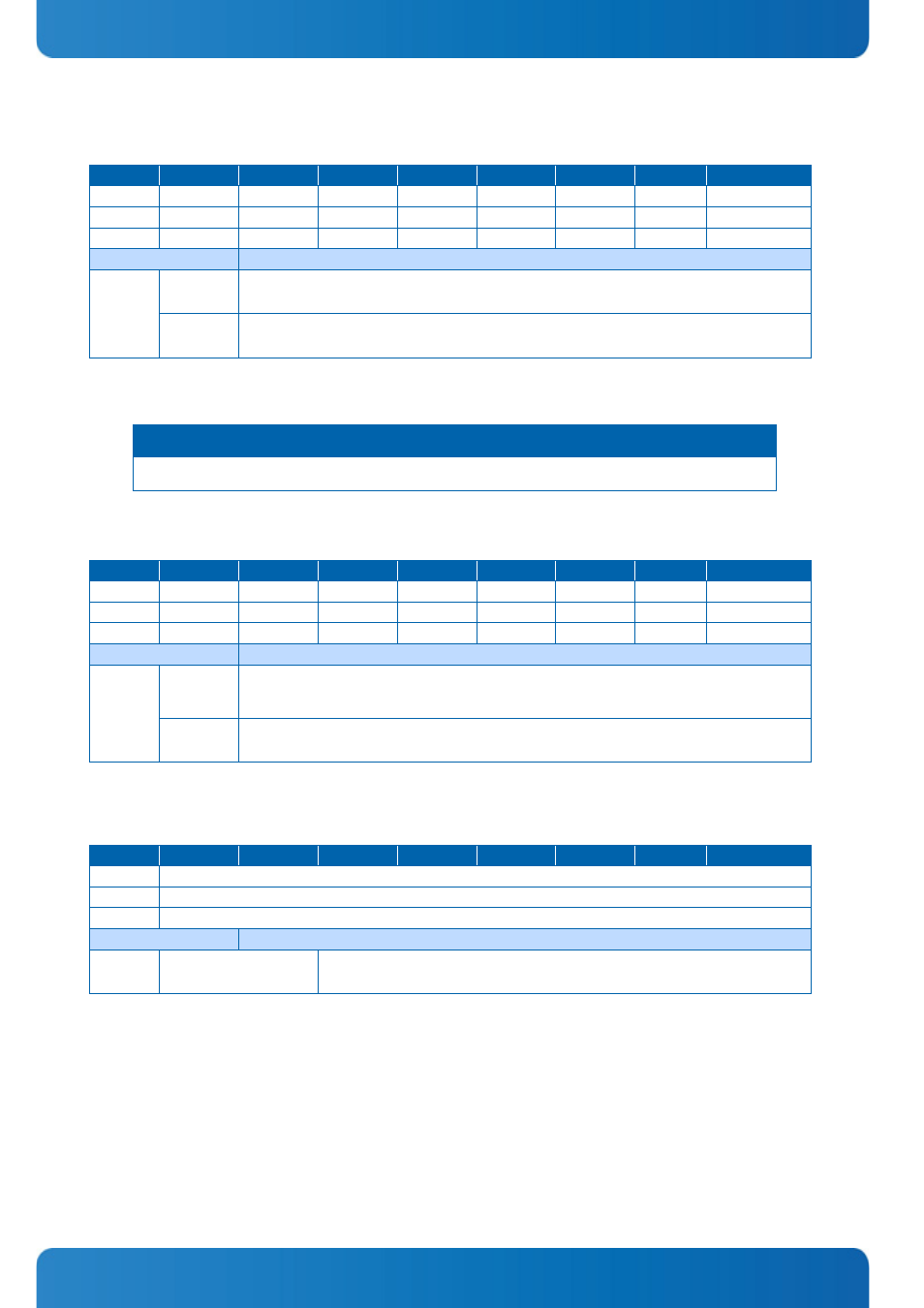

Table 3-53:

0x30E: Default Core1 Speed Register (Reserved, see note!)

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

NU

cfg_core1_speed

WRITE

NU

NU

NU

NU

NU

NU

NU

NU

POWER UP

0

0

0

0

0

0

0

0

BITFIELD

DESCRIPTION

[D0]

0

Core 1 clock frequency is less than or equal to 1000 MHz.

1

Core 1 clock frequency is greater than 1000 MHz.

N O T I C E

Equivalent CPU strapping is hard coded in CPLD depends on board variant, read value is always 0xFE.

Table 3-54:

0x30F: Default SerDes PLL Time-out Enable Register

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

NU

NU

NU

NU

NU

NU

NU

cfg_srds_pll_toe

WRITE

NU

NU

NU

NU

NU

NU

NU

NU

POWER UP

0

0

0

0

0

0

0

0

BITFIELD

DESCRIPTION

[D0]

0

Enable PLL lock time-out counter. The power-on-reset sequence

waits for the SerDes PLL to lock while the time-out counter has not

expired.

1

Disable PLL lock time-out counter. The power-on-reset sequence

waits indefinately for the SerDes PLL to lock.

Table 3-55:

0x320-0x321: Scratchpad Registers #0-#1

ACTION

D7

D6

D5

D4

D3

D2

D1

D0

READ

Scratchpad#n

WRITE

Scratchpad#n

POWER UP

0xXX

BITFIELD

DESCRIPTION

[D0-D7]

Scratchpad#n

Scratchpad registers#0-#1