5 jitter attenuation, Cs8427 – Cirrus Logic CS8427 User Manual

Page 59

CS8427

DS477F5

59

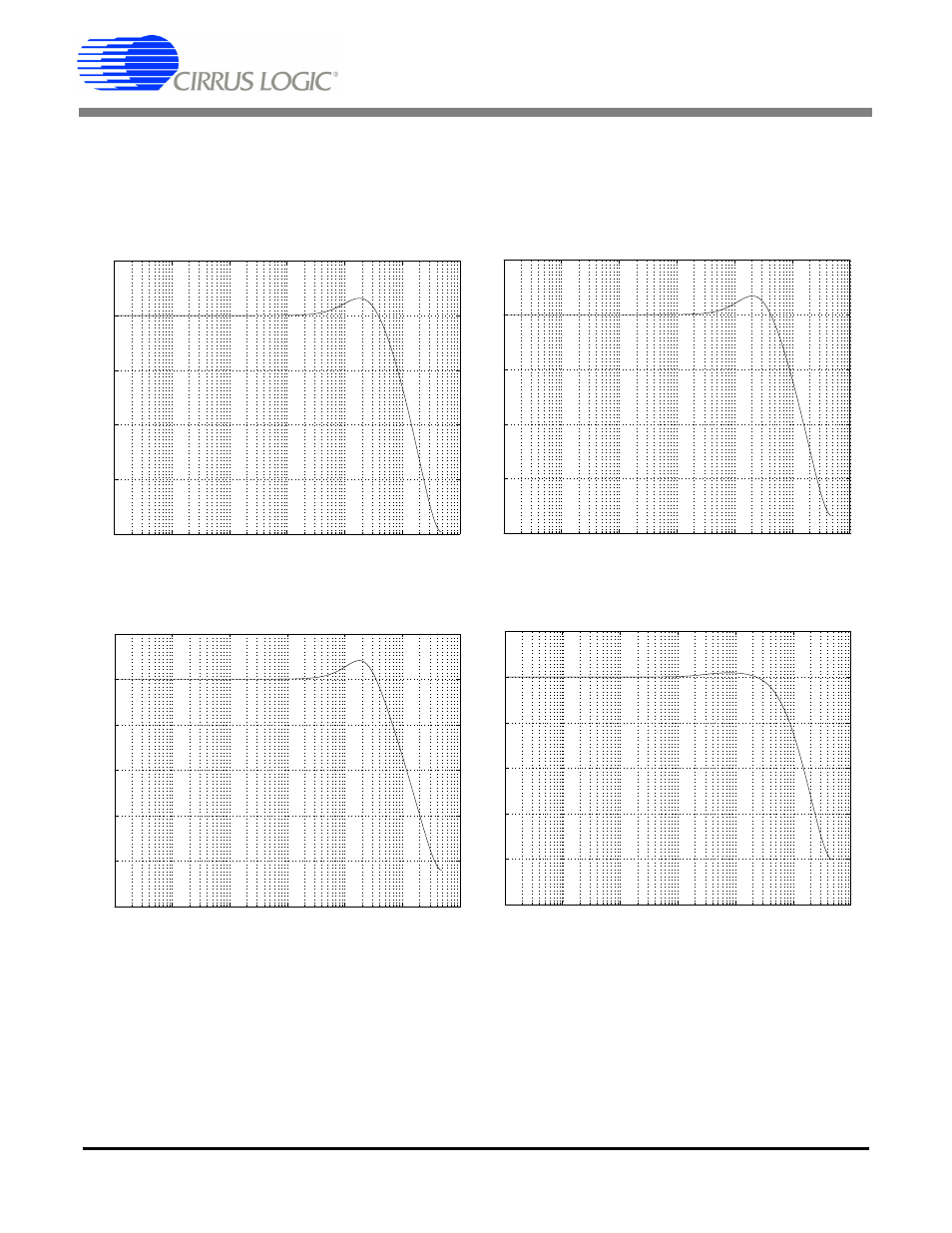

20.3.5 Jitter Attenuation

Shown in Figure 33, Figure 34, Figure 35, and Fig-

ure 36 are jitter attenuation plots for the various re-

visions of the CS8427 when used with the

appropriate external PLL component values (as

noted in Table 7). The AES3 and IEC60958-4

specifications do not have allowances for locking

to sample rates less than 32 kHz or for locking to

the ILRCK input. These specifications state a max-

imum of 2 dB jitter gain or peaking.

10

−1

10

0

10

1

10

2

10

3

10

4

10

5

−20

−15

−10

−5

0

5

Jitter Frequency (Hz)

Jitter Attenuation (dB)

10

−1

10

0

10

1

10

2

10

3

10

4

10

5

−20

−15

−10

−5

0

5

Jitter Frequency (Hz)

Jitter Attenuation (dB)

10

−1

10

0

10

1

10

2

10

3

10

4

10

5

−25

−20

−15

−10

−5

0

5

Jitter Frequency (Hz)

Jitter Attenuation (dB)

10

−1

10

0

10

1

10

2

10

3

10

4

10

5

−25

−20

−15

−10

−5

0

5

Jitter Frequency (Hz)

Jitter Attenuation (dB)

Figure 33. Revision A

Figure 34. Revision A1

Figure 35. Revision A2 using A1 values

Figure 36. Revision A2 using A2* values

- CobraNet (147 pages)

- CS4961xx (54 pages)

- CS150x (8 pages)

- CS1501 (16 pages)

- CS1601 (2 pages)

- CS1601 (16 pages)

- CS1610 (16 pages)

- CRD1610-8W (24 pages)

- CRD1611-8W (25 pages)

- CDB1610-8W (21 pages)

- CS1610A (18 pages)

- CDB1611-8W (21 pages)

- CDB1610A-8W (21 pages)

- CDB1611A-8W (21 pages)

- CRD1610A-8W (24 pages)

- CRD1611A-8W (25 pages)

- CS1615 (16 pages)

- AN403 (15 pages)

- AN401 (14 pages)

- AN400 (15 pages)

- AN375 (27 pages)

- AN376 (9 pages)

- CRD1615-8W (22 pages)

- CRD1616-8W (23 pages)

- AN402 (14 pages)

- AN404 (15 pages)

- CRD1615A-8W (21 pages)

- CS1615A (16 pages)

- CS1630 (56 pages)

- AN374 (35 pages)

- AN368 (80 pages)

- CRD1630-10W (24 pages)

- CRD1631-10W (25 pages)

- CS1680 (16 pages)

- AN405 (13 pages)

- AN379 (31 pages)

- CRD1680-7W (31 pages)

- AN335 (10 pages)

- AN334 (6 pages)

- AN312 (14 pages)

- AN Integrating CobraNet into Audio Products (16 pages)

- CobraNet Audio Routing Primer (9 pages)

- Bundle Assignments in CobraNet Systems (3 pages)

- CS2300-01 (3 pages)

- CS2000-CP (38 pages)