4 aes3 and s/pdif standards documents, Data i/o flow and clocking options, Figure 6. cs8427 internal block diagram – Cirrus Logic CS8427 User Manual

Page 13: Cs8427

CS8427

DS477F5

13

Channel Status bits. The part also has a feature

that allows the first five bytes of Channel Status

memory to be configured and transmitted in each

channel status block without change. See

dix A: External AES3/SPDIF/IEC60958 Transmit-

ter and Receiver Components” on page 50

tutorial in Channel Status and User bit manage-

ment.

3.4

AES3 and S/PDIF Standards

Documents

This data sheet assumes that the user is familiar

with the AES3 and S/PDIF data formats. It is advis-

able to have current copies of the AES3 and

IEC60958 specifications on hand for easy refer-

ence.

s.org

www.ansi.org

www.iec.ch

. The latest

EIAJ CP-1201 standard is available from the Jap-

anese Electronics Bureau.

Crystal Application Note AN22: Overview of Digital

Audio Interface Data Structures contains a useful

tutorial on digital audio specifications, but it should

not be considered a substitute for the standards.

The paper, An Understanding and Implementation

of the SCMS Serial Copy Management System for

Digital Audio Transmission, by Clifton Sanchez, is

an excellent tutorial on SCMS. It is available from

the AES as preprint 3518.

4. DATA I/O FLOW AND CLOCKING

OPTIONS

The CS8427 can be configured for several connec-

tivity alternatives, called data flows.

ware Mode Audio Data Flow Switching Options” on

page 19

shows the data flow switching, along with

the control register bits which control the switches;

this drawing only shows the audio data paths for

simplicity. This drawing only shows the audio data

paths for simplicity.

shows the internal

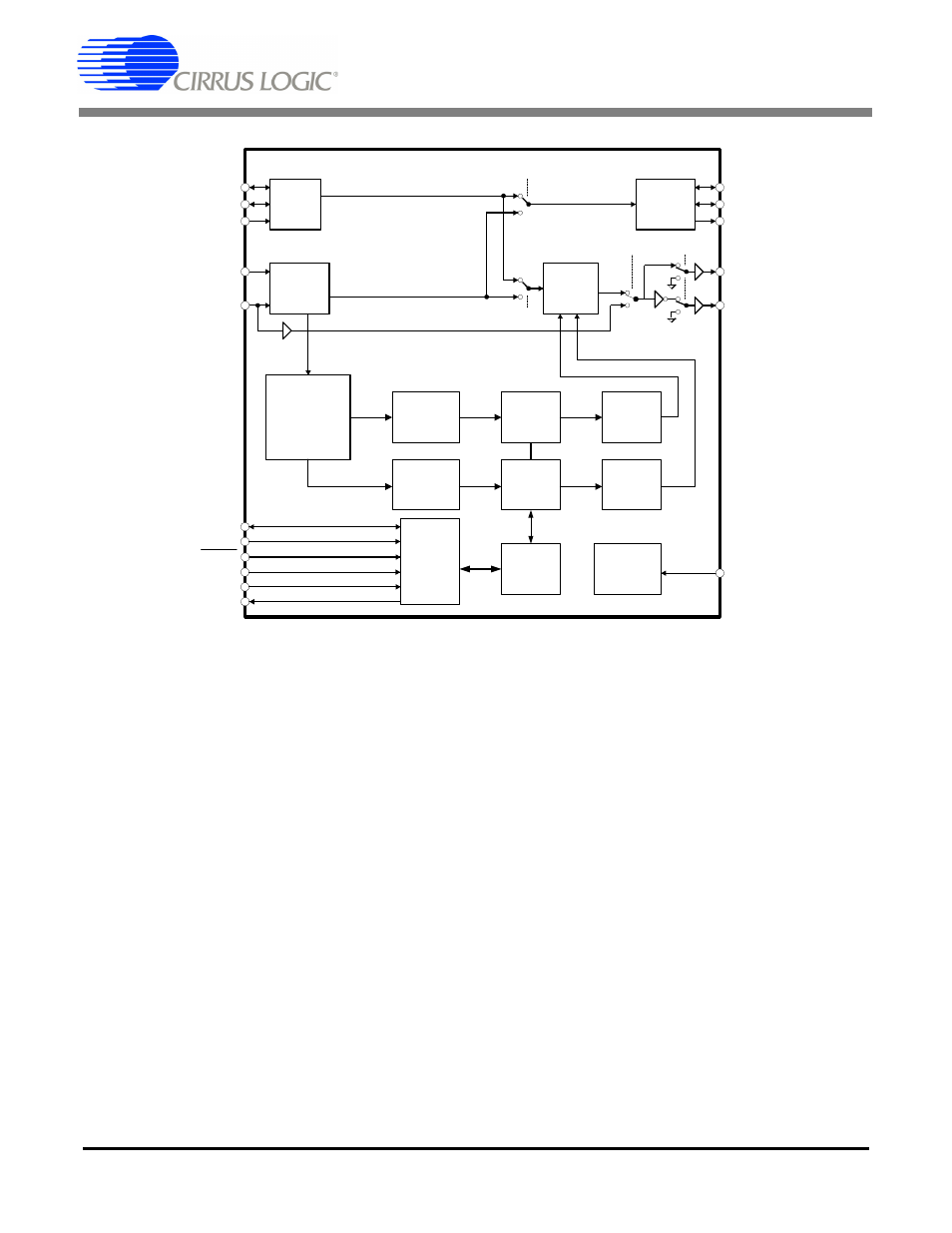

Figure 6. CS8427 Internal Block Diagram

Serial

Audio

Input

AES3

Encoder

Serial

Audio

Output

Receiver

RXP

RXN

ILRCK

ISCLK

SDIN

OLRCK

OSCLK

SDOUT

TXP

TXN

AES3

TXOFF

AESBP

SPD1-0

TXD1-0

Channel

Status

and

User Data

Recovery

Control

Port

Control

Registers

Channel

Status Bits

D

User Bits

D

E

F

E

F

SDA/CDOUT

SCL/CCLK

AD1/CDIN

AD0/CS

INT

Output

Clock

Generator

OMCK

AD2/EMPH