Cs8427, 8 interrupt 2 status (08h) (read only), 9 interrupt 1 mask (09h) – Cirrus Logic CS8427 User Manual

Page 33

CS8427

DS477F5

33

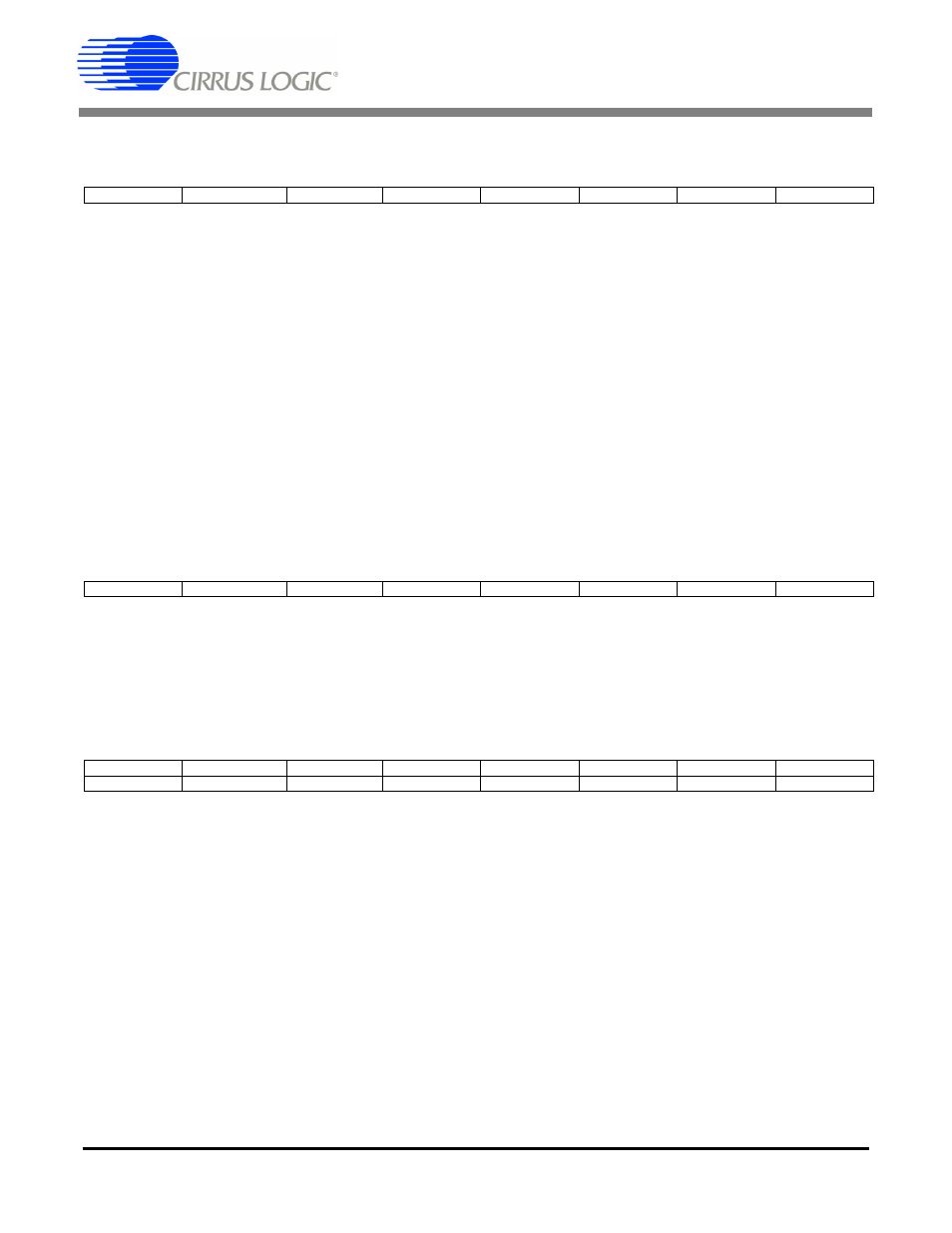

11.8 Interrupt 2 Status (08h) (Read Only)

For all bits in this register, a “1” means the associated interrupt condition has occurred at least once since the register

was last read. A ”0” means the associated interrupt condition has NOT occurred since the last reading of the register.

Reading the register resets all bits to 0, unless the interrupt mode is set to level and the interrupt source is still true.

Status bits that are masked off in the associated mask register will always be “0” in this register. This register defaults

to 00h.

DETU - D to E U-buffer transfer interrupt. (Block Mode only)

Indicates the completion of a D to E U-buffer transfer. See “Channel Status and User Data Buffer Man-

agement” on page 51 for more information.

EFTU - E to F U-buffer transfer interrupt. (Block Mode only)

Indicates the completion of a E to F U-buffer transfer. See “Channel Status and User Data Buffer Man-

agement” on page 51 for more information.

QCH - A new block of Q-subcode data is available for reading.

The data must be completely read within 588 AES3 frames after the interrupt occurs to avoid corruption

of the data by the next block.

11.9 Interrupt 1 Mask (09h)

The bits of this register serve as a mask for the Interrupt 1 register. If a mask bit is set to 1, the error is unmasked,

meaning that its occurrence will affect the INT pin and the status register. If a mask bit is set to 0, the error is masked,

meaning that its occurrence will not affect the INT pin or the status register. The bit positions align with the corre-

sponding bits in the Interrupt 1 register. This register defaults to 00h.

11.10 Interrupt 1 Mode MSB (0Ah) & Interrupt 1 Mode LSB (0Bh)

The two Interrupt Mode registers form a 2-bit code for each Interrupt Register 1 function. There are three ways to

set the INT pin active in accordance with the interrupt condition. In the Rising edge active mode, the INT pin be-

comes active on the arrival of the interrupt condition. In the Falling edge active mode, the INT pin becomes active

on the removal of the interrupt condition. In Level active mode, the INT interrupt pin becomes active during the in-

terrupt condition. Be aware that the active level (Active High or Low) only depends on the INT[1:0] bits. These reg-

isters default to 00.

00 - Rising edge active

01 - Falling edge active

10 - Level active

11 - Reserved

7

6

5

4

3

2

1

0

0

0

0

0

DETU

EFTU

QCH

0

7

6

5

4

3

2

1

0

TSLIPM

OSLIPM

0

0

0

DETCM

EFTCM

RERRM

7

6

5

4

3

2

1

0

TSLIP1

OSLIP1

0

0

0

DETC1

EFTC1

RERR1

TSLIP0

OSLIP0

0

0

0

DETC0

EFTC0

RERR0