Cirrus Logic CS8416 User Manual

192 khz digital audio interface receiver, Cs8416, Features

Copyright

© Cirrus Logic, Inc. 2007

(All Rights Reserved)

192 kHz Digital Audio Interface Receiver

Features

Complete EIAJ CP1201, IEC-60958, AES3,

S/PDIF-Compatible Receiver

+3.3 V Analog Supply (VA)

+3.3 V Digital Supply (VD)

+3.3 V or +5.0 V Digital Interface Supply (VL)

8:2 S/PDIF Input MUX

AES/SPDIF Input Pins Selectable in Hardware

Mode

Three General Purpose Outputs (GPO) Allow

Signal Routing

Selectable Signal Routing to GPO Pins

S/PDIF-to-TX Inputs Selectable in Hardware

Mode

Flexible 3-wire Serial Digital Output Port

32 kHz to 192 kHz Sample Frequency Range

Low-Jitter Clock Recovery

Pin and Microcontroller Read Access to

Channel Status and User Data

SPI™ or I²C

®

Control Port Software Mode and

Stand-Alone Hardware Mode

Differential Cable Receiver

On-Chip Channel Status Data Buffer Memories

Auto-Detection of Compressed Audio Input

Streams

Decodes CD Q Sub-Code

OMCK System Clock Mode

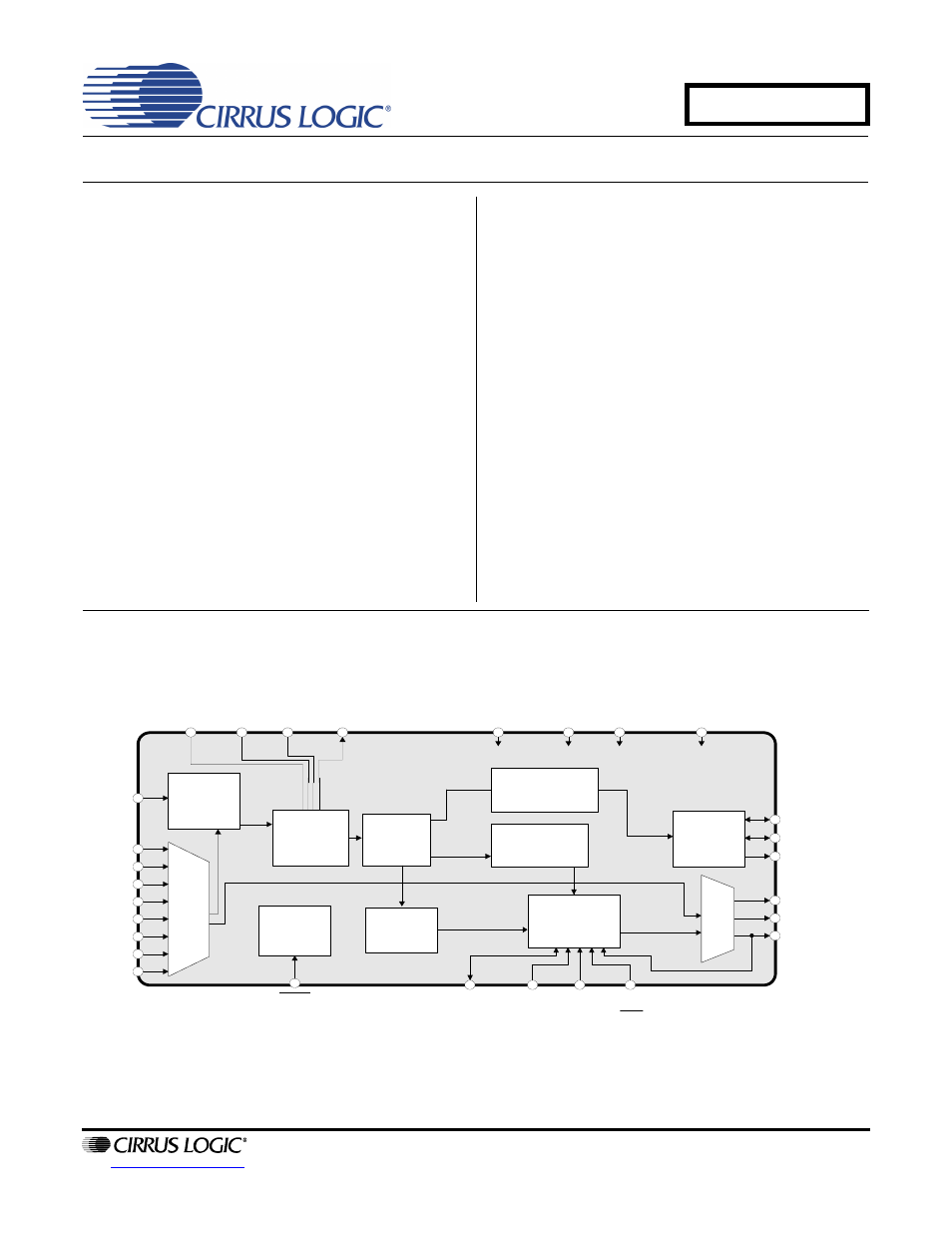

See the

Clock &

Data

Recovery

Misc.

Control

Serial

Audio

Output

Receiver

AES3

S/PDIF

Decoder

Control

Port &

Registers

RXN

RXP1

OLRCK

OSCLK

SDOUT

RST

SDA/

CDOUT

SCL/

CCLK

AD1/

CDIN

AD0/

CS

AGND FILT

VL DGND

RMCK

RXP2

RXP3

RXP4

RXP5

RXP6

RXP7

8:2

MUX

OMCK

GPO0

GPO1

AD2/GPO2

RXP0

n:3

MUX

VD

VA

TX Passthrough

Format

Detect

C & U bit

Data Buffer

De-emphasis

Filter

AUGUST '07

DS578F3

CS8416

Document Outline

- 1. Characteristics and Specifications

- Specified Operating Conditions

- Absolute Maximum Ratings

- DC Electrical Characteristics

- Digital Input Characteristics

- Digital Interface Specifications

- Switching Characteristics

- Switching Characteristics - Serial Audio Ports

- Switching Characteristics - Control Port - SPI Mode

- Switching Characteristics - Control Port- I·C Format

- 2. Pin Description - Software Mode

- 3. Pin Description - Hardware Mode

- 4. Typical Connection Diagrams

- 5. Applications

- 6. General Description

- 7. Serial Audio Output Port

- 8. S/PDIF Receiver

- 9. General Purpose Outputs

- 10. Error and Status Reporting

- 11. Channel Status and User-Data Handling

- 12. Control Port Description

- 13. Control Port Register Quick Reference

- 14. Control Port Register Descriptions

- 14.1 Memory Address Pointer (MAP)

- 14.2 Control0 (00h)

- 14.3 Control1 (01h)

- 14.4 Control2 (02h)

- 14.5 Control3 (03h)

- 14.6 Control4 (04h)

- 14.7 Serial Audio Data Format (05h)

- 14.8 Receiver Error Mask (06h)

- 14.9 Interrupt Mask (07h)

- 14.10 Interrupt Mode MSB (08h) and Interrupt Mode LSB(09h)

- 14.11 Receiver Channel Status (0Ah)

- 14.12 Format Detect Status (0Bh)

- 14.13 Receiver Error (0Ch)

- 14.14 Interrupt 1 Status (0Dh)

- 14.15 Q-Channel Subcode (0Eh - 17h)

- 14.16 OMCK/RMCK Ratio (18h)

- 14.17 Channel Status Registers (19h - 22h)

- 14.18 IEC61937 PC/PD Burst Preamble (23h - 26h)

- 14.19 CS8416 I.D. and Version Register (7Fh)

- 15. Hardware Mode

- 16. External AES3/SPDIF/IEC60958 Receiver Components

- 17. Channel Status Buffer Management

- 18. PLL Filter

- 19. Package Dimensions

- 20. Ordering Information

- 21. Revision History