2 aes11 behavior, Table 1. typical delays by frequency values, Cs8416 – Cirrus Logic CS8416 User Manual

Page 26

26

DS578F3

CS8416

7.2

AES11 Behavior

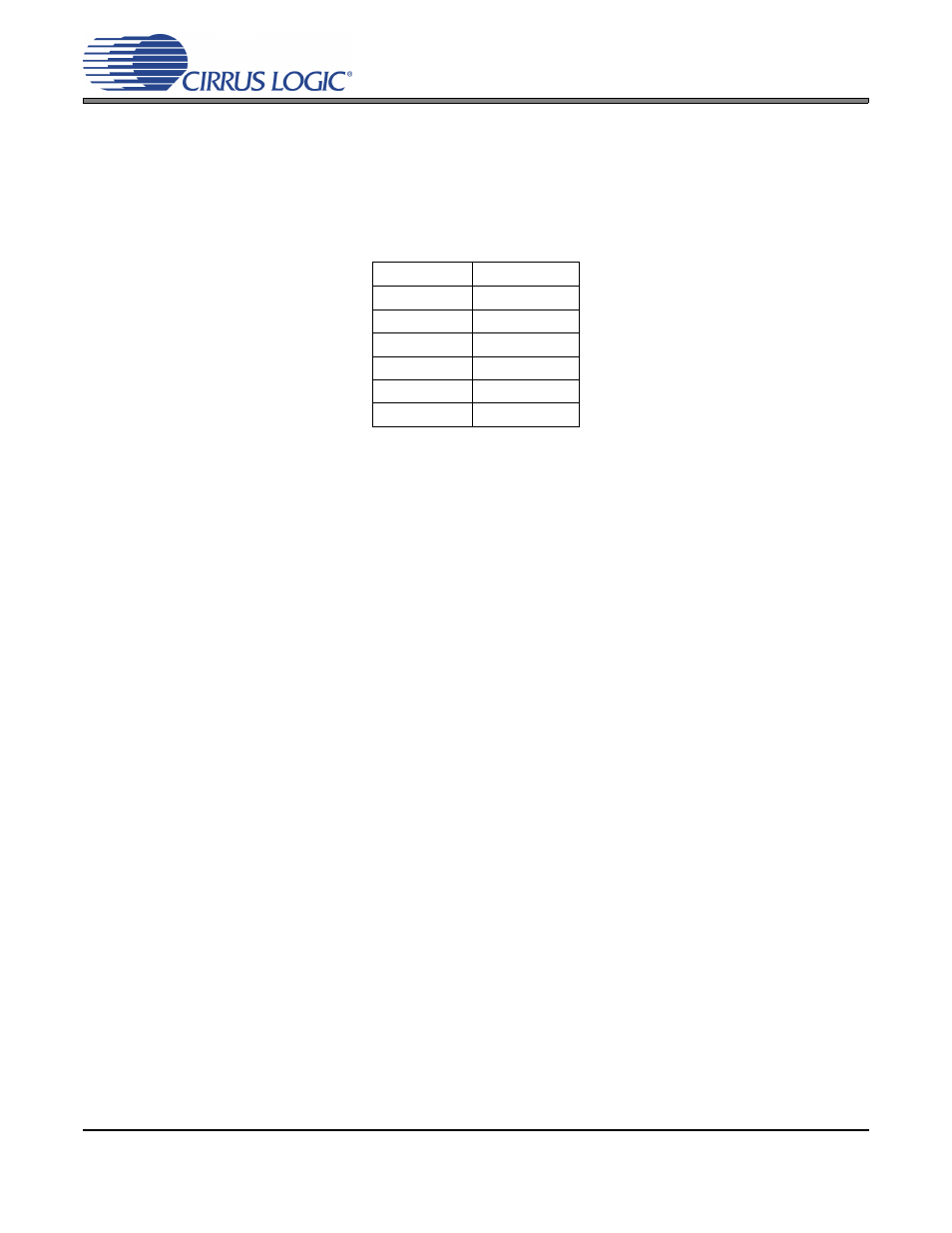

When OLRCK is configured as a master, the positive or negative edge of OLRCK (depending on the setting

of SOLRPOL in register 05h) will be within -1.0%(1/Fs) to 1.1%(1/Fs) from the start of the preamble X/Z. In

master mode, the latency through the part is dependent on the input sample frequency. The typical delay

through the part from the beginning of the preamble to the active edge of OLRCK for the various sample

frequencies is given in

. In master mode without the de-emphasis filter engaged, the latency of the

audio data will be 3 frames.

When OLRCK is configured as a slave, any synchronized input within +/-28%(1/Fs) from the positive or neg-

ative edge of OLRCK (depending on the setting of SOLRPOL in register 05h) will be treated as being sam-

pled at the same time. Since the CS8416 has no control of the OLRCK in slave mode, the latency of the

data through the part will be a multiple of 1/Fs plus the delay between OLRCK and the preambles.

Both of these conditions are within the tolerance range set forth in the AES11 standard.

Fs (kHz)

Delay (ns)

32

98.0

44.1

80.5

48

78.0

64

67.0

96

57.5

192

47.0

Table 1. Typical Delays by Frequency Values