2 qfn pin description, Cs8416 – Cirrus Logic CS8416 User Manual

Page 14

14

DS578F3

CS8416

2.2

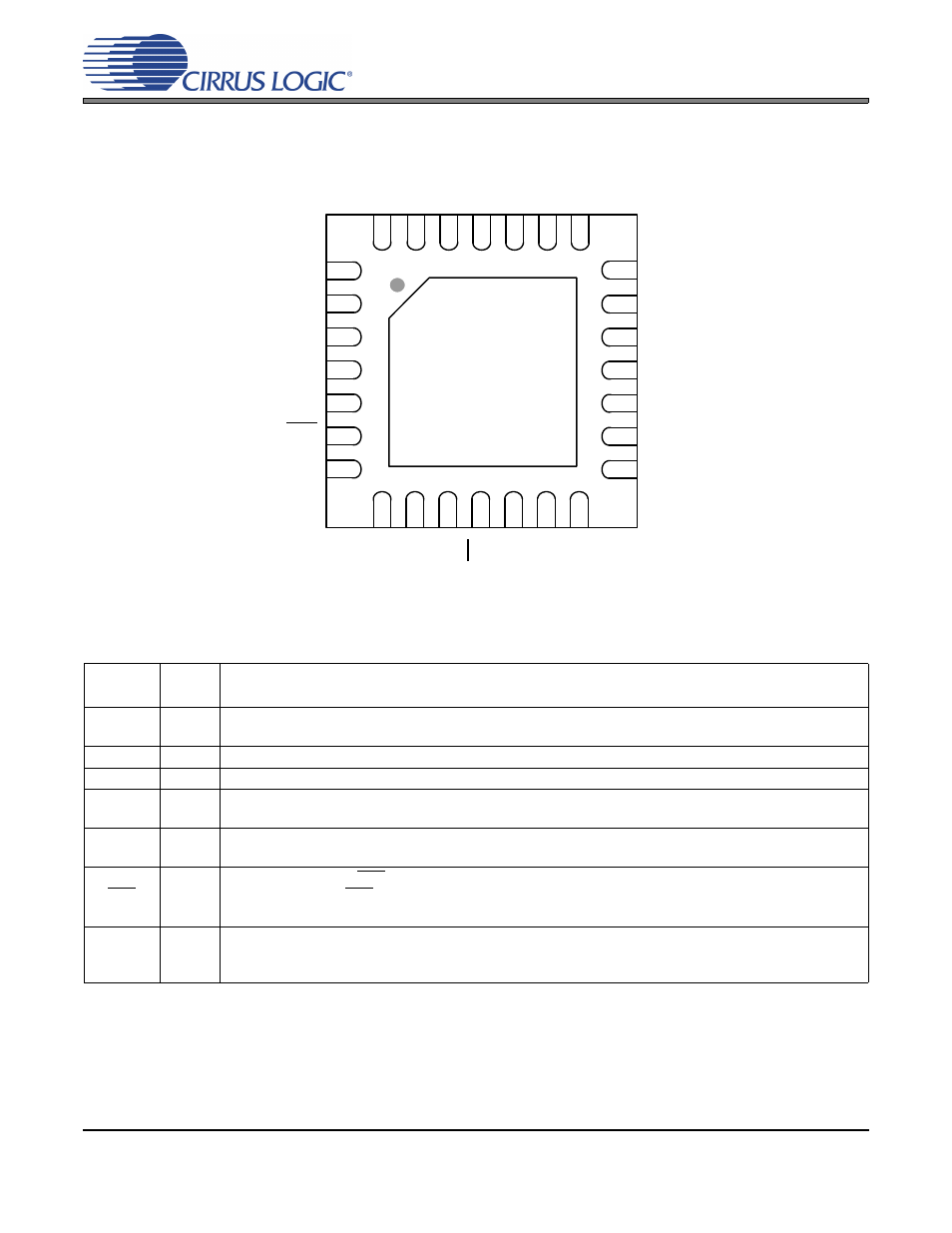

QFN Pin Description

Pin

Name

Pin #

Pin Description

VA

3

Analog Power (Input) - Analog power supply. Nominally +3.3 V. This supply should have as little noise

as possible since noise on this pin will directly affect the jitter performance of the recovered clock

VD

20

Digital Power (Input) – Digital core power supply. Nominally +3.3 V

VL

18

Logic Power (Input) – Input/Output power supply. Nominally +3.3 V or +5.0 V

AGND

4

Analog Ground (Input) - Ground for the analog circuitry in the chip. AGND and DGND should be con-

nected to a common ground area under the chip.

DGND

19

Digital & I/O Ground (Input) - Ground for the I/O and core logic. AGND and DGND should be connected

to a common ground area under the chip.

RST

6

Reset (Input) - When RST is low, the CS8416 enters a low power mode and all internal states are reset.

On initial power up, RST must be held low until the power supply is stable, and all input clocks are stable

in frequency and phase.

FILT

5

PLL Loop Filter (Output) - An RC network should be connected between this pin and analog ground.

For minimum PLL jitter, return the ground end of the filter network directly to AGND. See

for more information on the PLL and the external components.

9

8

7

6

5

4

3

2

1

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

Top-Down View

28-pin QFN Package

Thermal Pad

RXP

1

RXP

2

RXP

3

OL

RCK

OSCLK

SDOUT

OM

CK

RXP

5

RXP

6

RXP

7

AD0 / CS

AD1 / CDIN

SCL / CCLK

SDA /

CDOUT

RXP0

RXN

VA

AGND

FILT

RST

RXP4

RMCK

VD

DGND

VL

GPO0

GPO1

AD2 / GPO2