Typical connection diagrams – Cirrus Logic CS8416 User Manual

Page 20

20

DS578F3

CS8416

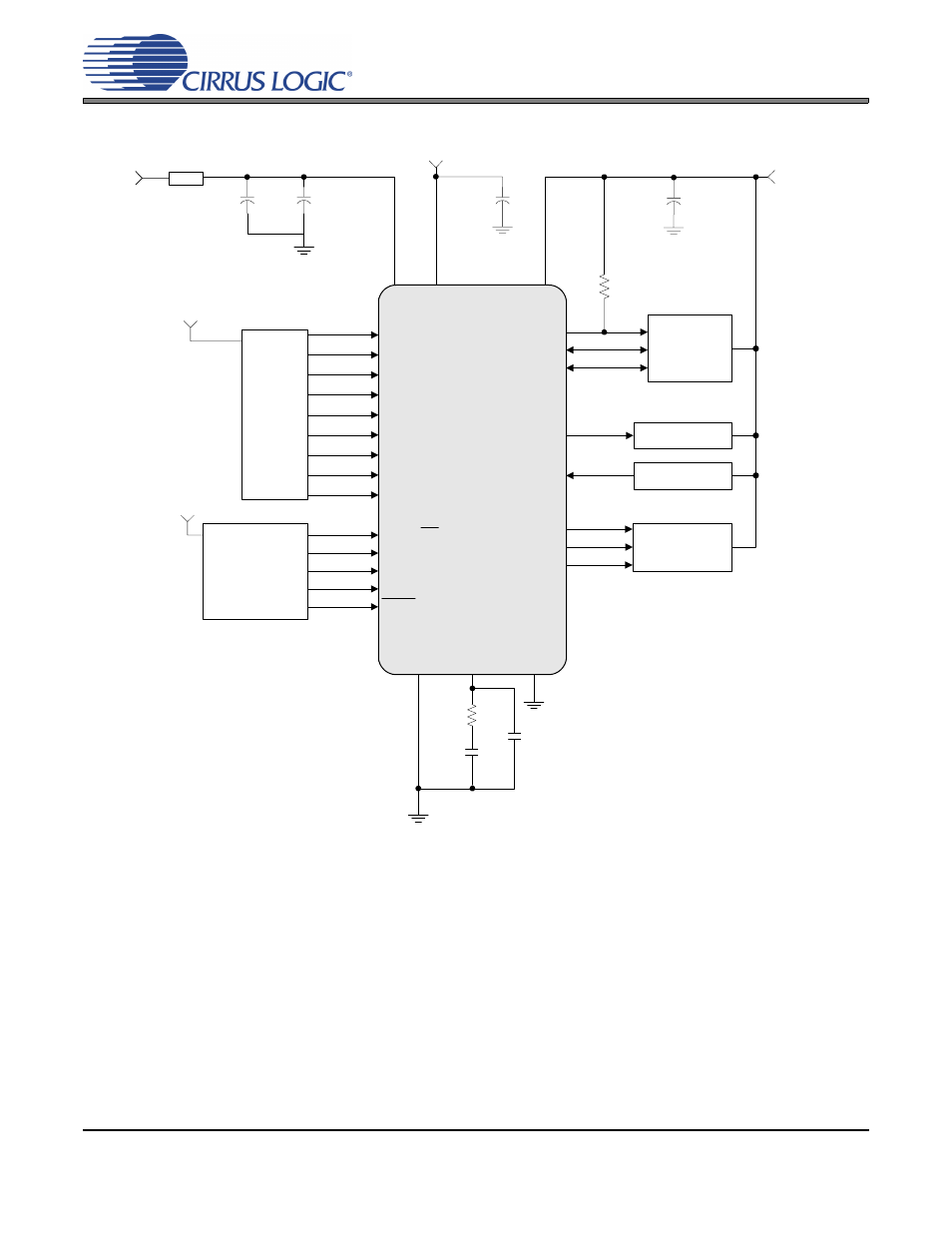

4. TYPICAL CONNECTION DIAGRAMS

Figure 5. Typical Connection Diagram - Software Mode

* A separate analog supply is only necessary in applications where RMCK is used for a jitter sensitive task. For

applications where RMCK is not used for a jitter sensitive task, connect VA to VD via a ferrite bead. Keep decou-

pling capacitors between VA and AGND.

** See

and

“External AES3/SPDIF/IEC60958 Receiver Components” on page 49

for typical input configurations and recommended input circuits.

*** For best jitter performance, connect the filter ground directly to the AGND pin. See

for PLL

filter values.

CS8416

FILT

DGND

AGND

**

***

RXN

RXP0

RXP1

RXP2

RXP3

AES3 /

S/PDIF

Sources

Microcontroller

SCL / CCLK

SDA / CDOUT

OMCK

Clock Source

RST

AD1 / CDIN

GPO0

RMCK

Clock Control

Serial Audio

Input

Device

OLRCK

OSCLK

SDOUT

External

Interface

RXP4

RXP5

RXP6

RXP7

AD0 / CS

GPO1

AD2/GPO2

R

FLT

C

FLT

C

RIP

47k

Ω

10 F

μ

+3.3 V or +5 V

0.1 F

μ

+3.3 V

Ferrite

Bead

+3.3 V

Analog

Supply

*

VA

VD

VL

*

0.1 F

μ

0.1 F

μ

VL

VL