14 interrupt 1 status (0dh), 15 q-channel subcode (0eh - 17h), Cs8416 – Cirrus Logic CS8416 User Manual

Page 44

44

DS578F3

CS8416

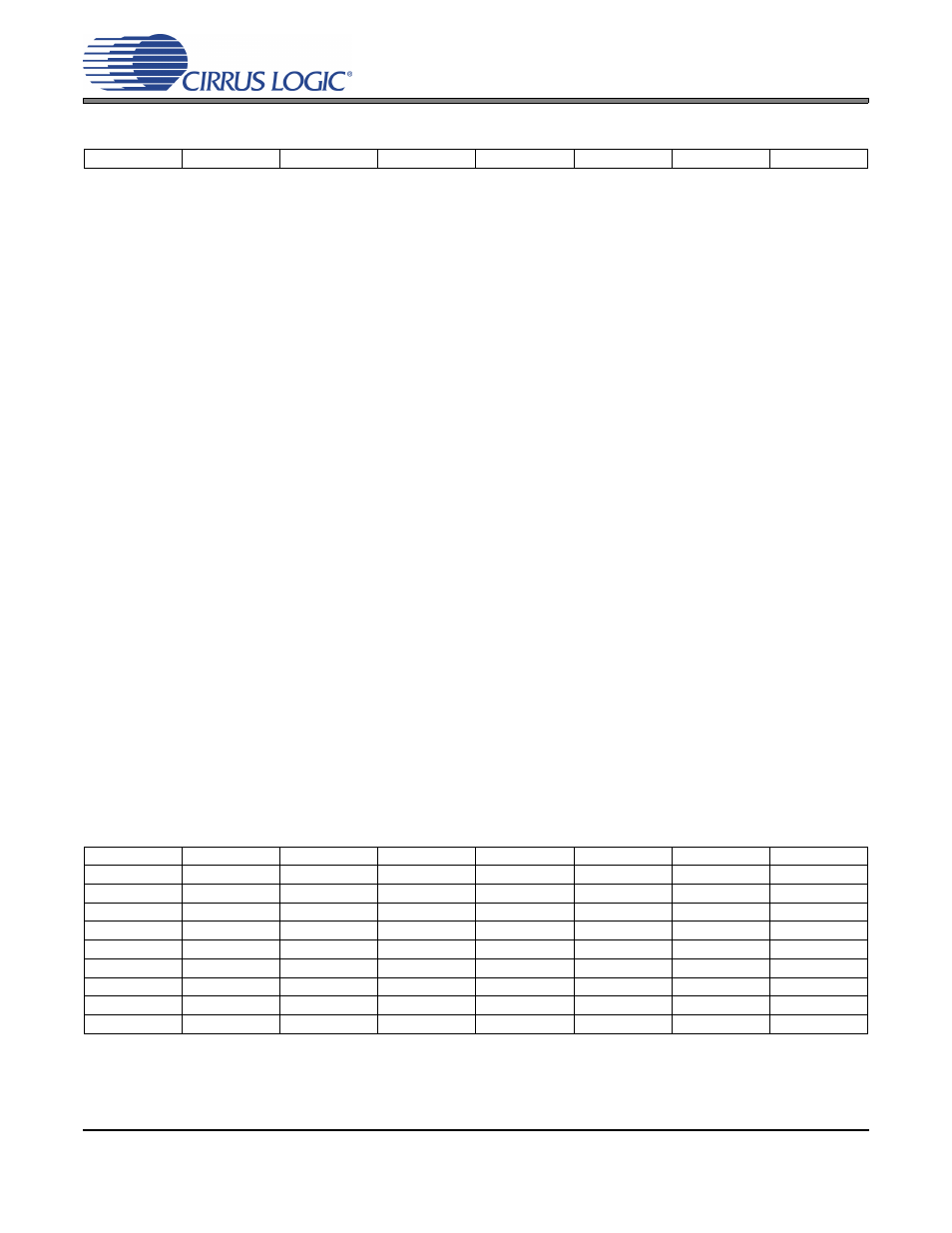

14.14 Interrupt 1 Status (0Dh)

For all bits in this register, a “1” means the associated interrupt condition has occurred at least once since

the register was last read. A “0” means the associated interrupt condition has NOT occurred since the last

reading of the register. Reading the register resets all bits to 0, unless the interrupt mode is set to level and

the interrupt source is still true. Status bits that are masked off in the associated mask register will always

be “0” in this register.

PCCH

– PC burst preamble change.

Indicates that the PC byte has changed from its previous value. If the IEC61937 bit in the Format Detect

Status register goes high, it will cause a PCCH interrupt even if the PC byte hasn’t changed since the last

time the IEC61937 bit went high.

OSLIP

- Serial audio output port data slip interrupt

When the serial audio output port is in slave mode, and OLRCK is asynchronous to the port data source,

this bit will go high every time a data sample is dropped or repeated. See

for more information.

DETC

- D to E C-buffer transfer interrupt.

Indicates the completion of a D to E C-buffer transfer. See

“Channel Status Buffer Management” on

.

C_CHANGE

-Indicates that the current 10 bytes of channel status is different from the previous 10 bytes.

(5 bytes per channel)

RERR

- A receiver error has occurred.

The Receiver Error register may be read to determine the nature of the error which caused the interrupt.

QCH

– A new block of Q-subcode is available for reading. The data must be read within 588 AES3 frames

after the interrupt occurs to avoid corruption of the data by the next block.

FCH

– Format Change: Goes high when the PCM, IEC61937, DTS_LD, DTS_CD, or DGTL_SIL bits in the

Format Detect Status register transition from 0 to 1. When these bits in the Format Detect Status register

transition from 1 to 0, an interrupt will not be generated.

14.15 Q-Channel Subcode (0Eh - 17h)

Each byte is LSB first with respect to the 80 Q-subcode bits Q[79:0]. Thus, bit 7 of address 0Eh is Q[0] while

bit 0 of address 0Eh is Q[7]. Similarly, bit 0 of address 17h corresponds to Q[79].

7

6

5

4

3

2

1

0

0

PCCH

OSLIP

DETC

CCH

RERR

QCH

FCH

7

6

5

4

3

2

1

0

CONTROL

CONTROL

CONTROL

CONTROL

ADDRESS

ADDRESS

ADDRESS

ADDRESS

TRACK

TRACK

TRACK

TRACK

TRACK

TRACK

TRACK

TRACK

INDEX

INDEX

INDEX

INDEX

INDEX

INDEX

INDEX

INDEX

MINUTE

MINUTE

MINUTE

MINUTE

MINUTE

MINUTE

MINUTE

MINUTE

SECOND

SECOND

SECOND

SECOND

SECOND

SECOND

SECOND

SECOND

FRAME

FRAME

FRAME

FRAME

FRAME

FRAME

FRAME

FRAME

ZERO

ZERO

ZERO

ZERO

ZERO

ZERO

ZERO

ZERO

ABS MINUTE ABS MINUTE ABS MINUTE ABS MINUTE ABS MINUTE ABS MINUTE ABS MINUTE ABS MINUTE

ABS SECOND ABS SECOND ABS SECOND ABS SECOND ABS SECOND ABS SECOND ABS SECOND ABS SECOND

ABS FRAME

ABS FRAME

ABS FRAME

ABS FRAME

ABS FRAME

ABS FRAME

ABS FRAME

ABS FRAME