Channel status and user-data handling, 1 software mode, 2 hardware mode – Cirrus Logic CS8416 User Manual

Page 32: Figure 10. c/u data outputs, 1 software mode 11.2 hardware mode

32

DS578F3

CS8416

11.CHANNEL STATUS AND USER-DATA HANDLING

“Channel Status Buffer Management” on page 51

describes Channel Status and User data control.

11.1 Software Mode

In Software Mode, several options are available for accessing the Channel Status and User data that is en-

coded in the received AES3/SPDIF stream.

The first option allows access directly through registers. The first 5 bytes of the Channel Status block are

decoded into the Receiver Channel Status Registers 19h - 22h. Registers 19h - 1Dh contain the A channel

status data. Registers 1Eh - 22h contain the B channel status data.

Received Channel Status (C), User (U), and EMPH bits may also be output to the GPO pins by appropriately

setting the GPOxSEL bits in control port registers 02h and 03h. In serial port master mode, OLRCK and

RCBL can be made available to qualify the U data output. In serial port slave mode, VLRCK and RCBL can

be made available to qualify the U data output. VLRCK is a virtual word clock, equal to the receiver recov-

ered sample rate, that can be used to frame the C/U output. VLRCK and RCBL are available through the

GPO pins.

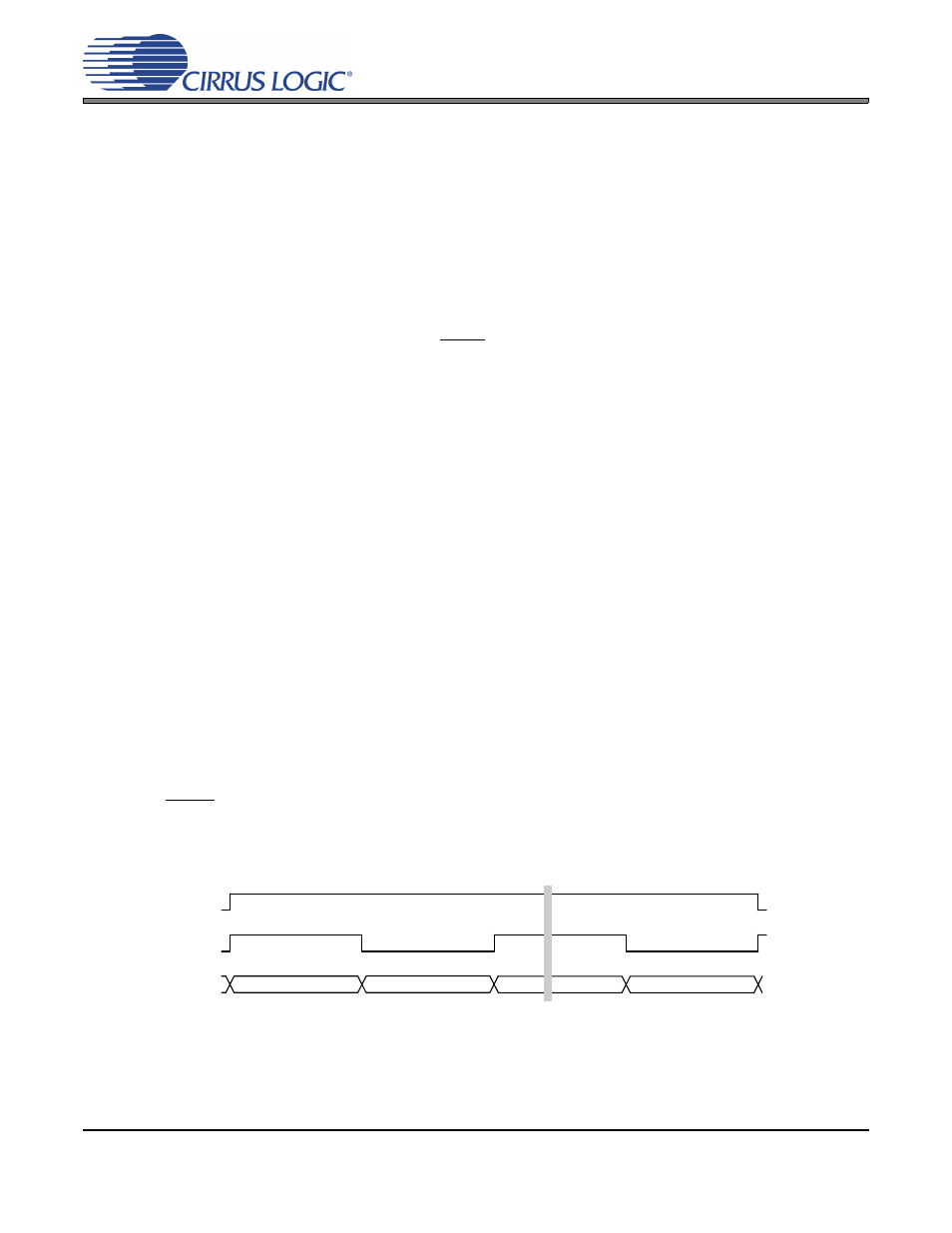

illustrates timing of the C and U data and their related signals.

The user may also access all of the C and U bits directly from the output data stream (SDOUT) by setting

bits SORES[1:0]=11 (AES3 Direct Mode) in the Serial Audio Data Format register (05h). The appropriate

bits can be stripped from the SDOUT signal by external control logic such as a DSP or microcontroller.

If the incoming User data bits have been encoded as Q-channel subcode, the data is decoded, buffered,

and presented in 10 consecutive register locations (0Eh-17h). An interrupt may be enabled to indicate the

decoding of a new Q-channel block, which may be read through the control port.

The encoded Channel Status bits which indicate sample word length are decoded according to AES3-1992

or IEC 60958. The number of auxiliary bits are reported in bits 7 to 4 of the Receiver Channel Status register

(0Ah).

11.2 Hardware Mode

In Hardware Mode, Received Channel Status (C), and User (U) bits are output on pins 19 and 18. In serial

port master mode, OLRCK and RCBL are made available to qualify the C and U data output.

lustrates timing of the C and U data and their related signals.

The user may also access all of the C and U bits directly from the output data stream (SDOUT) by pulling

the AUDIO and C pins high through 47 k

Ω resistors to VL (AES3 Direct Mode). The appropriate bits can be

stripped from the SDOUT signal by external control logic such as a DSP or microcontroller. Only OLRCK in

master mode is available to qualify the U output. See

“Hardware Mode Function Selection” on page 46

and

“Hardware Mode Equivalent Register Settings” on page 47

to configure these pins..

Figure 10. C/U Data Outputs

– RCBL goes high 2 frames after receipt of a Z preamble and is high for 16 frames.

– VLRCK is a virtual work clock, available through the GPO pins, that can be used

to frame the C/U output.

– VLRCK duty cycle is 50%. VLRCK frequency is always equal to the incoming

RCBL

(out)

VLRCK

(out)

C/U

(out)