2 capacitor selection, 3 circuit board layout, Figure 24. recommended layout example – Cirrus Logic CS8416 User Manual

Page 54: 4 component value selection, Table 6. external pll component values, For pll, Filter. in, Table 6, Cs8416

54

DS578F3

CS8416

18.2.2 Capacitor Selection

The type of capacitors used for the PLL filter can have a significant effect on receiver performance. Large

or exotic film capacitors are not necessary as their leads and the required longer circuit board traces add

undesirable inductance to the circuit. Surface mount ceramic capacitors are a good choice because their

own inductance is low, and they can be mounted close to the FILT pin to minimize trace inductance. For

C

RIP

, a C0G or NPO dielectric is recommended, and for C

FLT

, an X7R dielectric is preferred. Avoid ca-

pacitors with large temperature co-coefficient, or capacitors with high dielectric constants, that are sensi-

tive to shock and vibration. These include the Z5U and Y5V dielectrics.

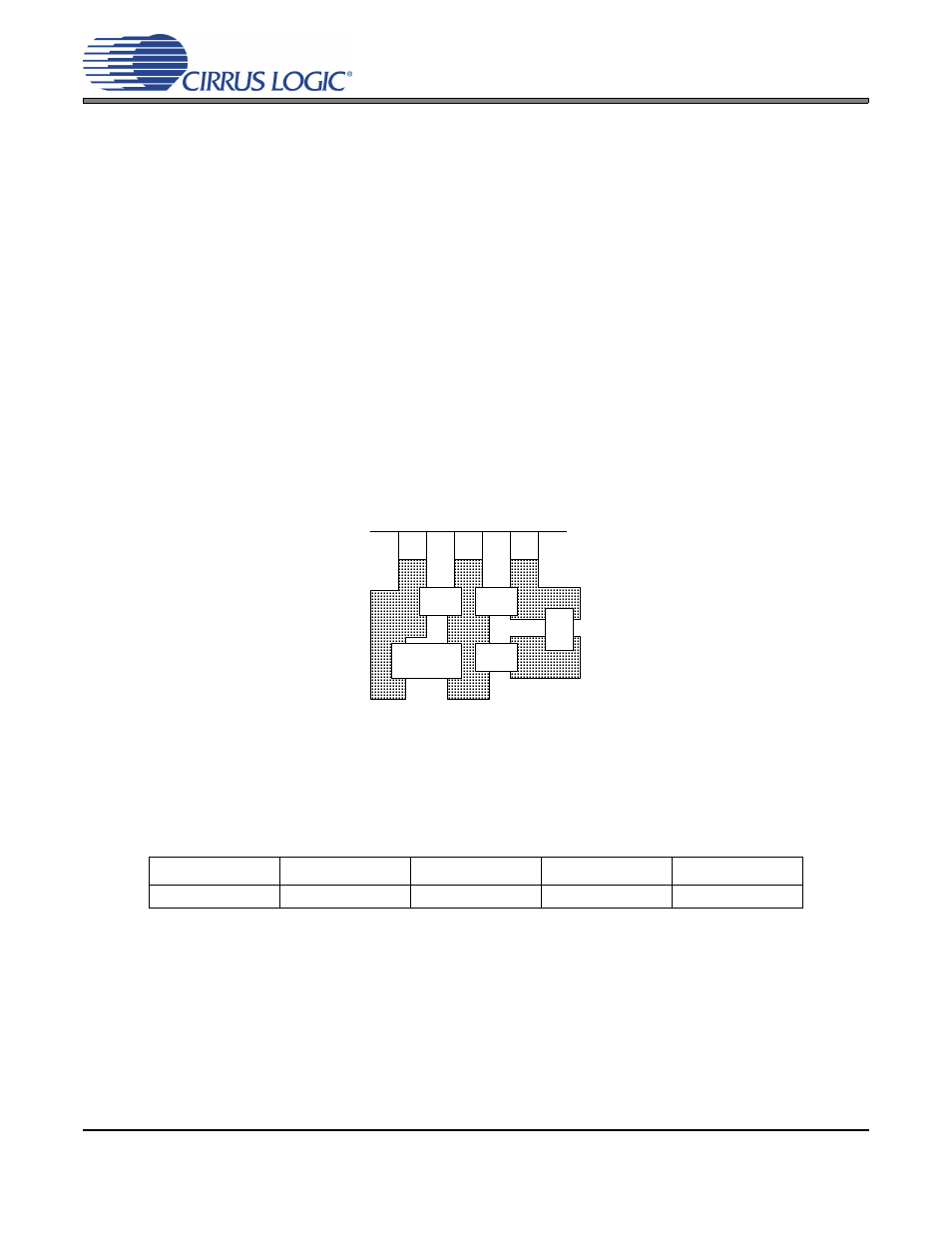

18.2.3 Circuit Board Layout

Board layout and capacitor choice affect each other and determine the performance of the PLL.

contains a suggested layout for the PLL filter components and for bypassing the analog supply voltage.

The 0.1 µF bypass capacitor is in a 1206 form factor. R

FLT

, C

FLT

, C

RIP

, and the 1000 pF decoupling ca-

pacitor are in an 0805 form factor. The traces are on the top surface of the board with the IC so that there

is no via inductance. The traces themselves are short to minimize the inductance in the filter path. The

VA and AGND traces extend back to their origin and are shown only in truncated form in the drawing.

18.2.4 Component Value Selection

The external PLL component values are listed in

Range (kHz)

R

FLT

C

FLT

C

RIP

Settling Time

32 - 192

3 k

Ω

22 nF

1 nF

4 ms

Table 6. External PLL Component Values

VA

AGN

D

FILT

C

FLT

1000

pF

.1µF

R

FLT

C

RIP

Figure 24. Recommended Layout Example