Cirrus Logic CS5490 User Manual

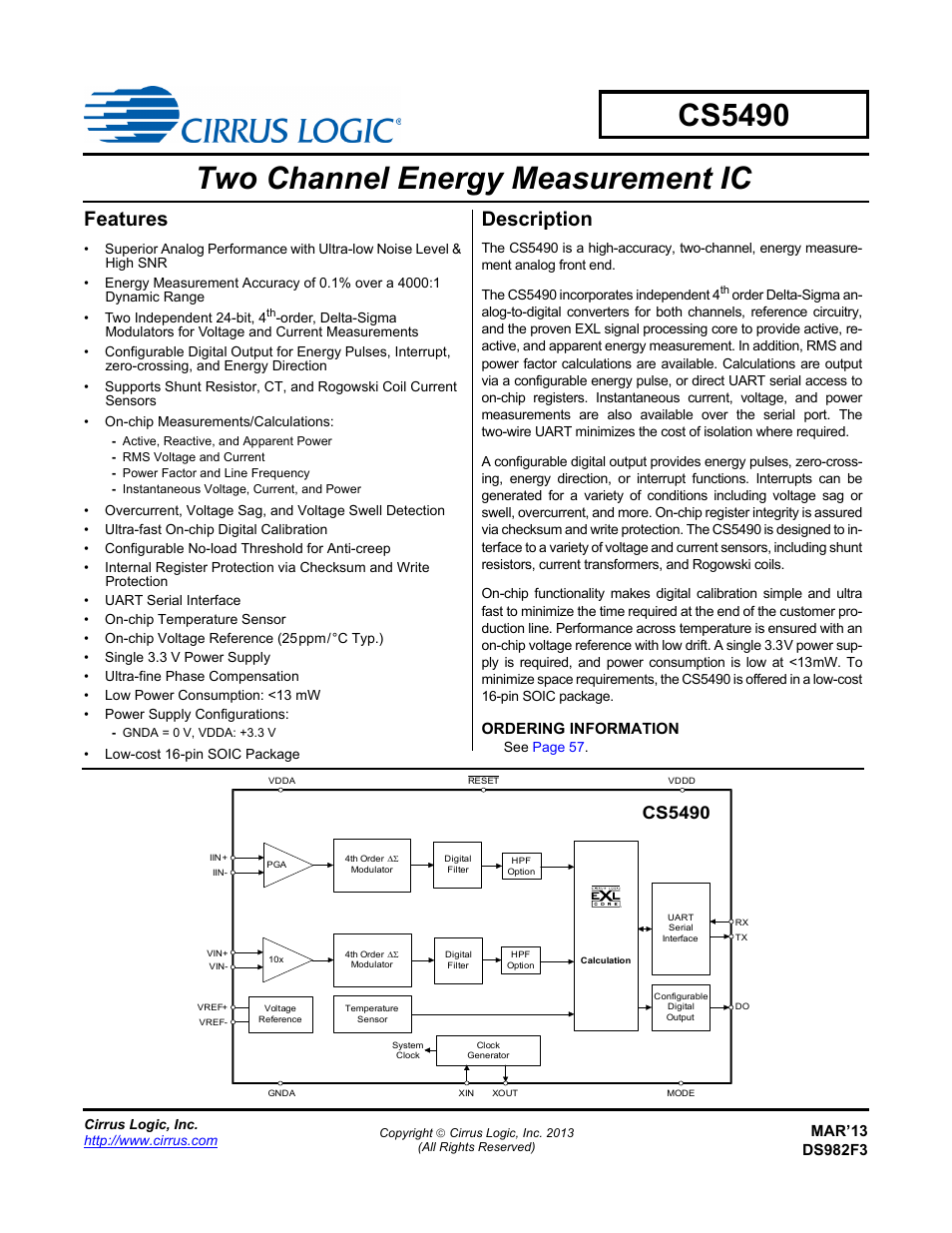

Cs5490 two channel energy measurement ic, Features, Description

Table of contents

Document Outline

- CS5490

- Two Channel Energy Measurement IC

- Features

- Description

- 1. Overview

- 2. Pin Description

- 3. Characteristics & Specifications

- 4. Signal Flow Description

- Figure 6. Signal Flow for V, I, P, and Q Measurements

- 4.1 Analog-to-Digital Converters

- 4.2 Decimation Filters

- 4.3 IIR Filter

- 4.4 Phase Compensation

- 4.5 DC Offset & Gain Correction

- 4.6 High-pass & Phase Matching Filters

- 4.7 Digital Integrators

- 4.8 Low-rate Calculations

- 4.9 Average Active Power Offset

- 4.10 Average Reactive Power Offset

- 5. Functional Description

- 6. Host Commands and Registers

- 6.1 Host Commands

- 6.2 Hardware Registers Summary (Page 0)

- 6.3 Software Registers Summary (Page 16)

- 6.4 Software Registers Summary (Page 17)

- 6.5 Software Registers Summary (Page 18)

- 6.6 Register Descriptions

- 6.6.1 Configuration 0 (Config0) – Page 0, Address 0

- 6.6.2 Configuration 1 (Config1) – Page 0, Address 1

- 6.6.3 Configuration 2 (Config2) – Page 16, Address 0

- 6.6.4 Phase Compensation (PC) – Page 0, Address 5

- 6.6.5 UART Control (SerialCtrl) – Page 0, Address 7

- 6.6.6 Pulse Output Width (PulseWidth) – Page 0, Address 8

- 6.6.7 Pulse Output Rate (PulseRate) – Page 18, Address 28

- 6.6.8 Pulse Output Control (PulseCtrl) – Page 0, Address 9

- 6.6.9 Register Lock Control (RegLock) – Page 0, Address 34

- 6.6.10 Phase Sequence Detection and Control (PSDC) – Page 0, Address 48

- 6.6.11 Checksum of Critical Registers (RegChk) – Page 16, Address 1

- 6.6.12 Interrupt Status (Status0) – Page 0, Address 23

- 6.6.13 Interrupt Mask (Mask) – Page 0, Address 3

- 6.6.14 Chip Status 1 (Status1) – Page 0, Address 24

- 6.6.15 Chip Status 2 (Status2) – Page 0, Address 25

- 6.6.16 Line to Sample Frequency Ratio (Epsilon) – Page 16, Address 49

- 6.6.17 No Load Threshold (LoadMIN) – Page 16, Address 58

- 6.6.18 Sample Count (SampleCount) – Page 16, Address 51

- 6.6.19 Cycle Count (CycleCount) – Page 18, Address 62

- 6.6.20 Filter Settling Time for Conversion Startup (TSETTLE ) – Page 16, Address 57

- 6.6.21 System Gain (SysGAIN ) – Page 16, Address 60

- 6.6.22 Rogowski Coil Integrator Gain (IntGAIN ) – Page 18, Address 43

- 6.6.23 System Time (Time) – Page 16, Address 61

- 6.6.24 Voltage Sag Duration (VSagDUR ) – Page 17, Address 0

- 6.6.25 Voltage Sag Level (VSagLEVEL ) – Page 17, Address 1

- 6.6.26 Current Overcurrent Duration (IOverDUR ) – Page 17, Address 4

- 6.6.27 Current Overcurrent Level (IOverLEVEL ) – Page 17, Address 5

- 6.6.28 Voltage Swell Duration (VSwellDUR ) – Page 18, Address 46

- 6.6.29 Voltage Swell Level (VSwellLEVEL ) – Page 18, Address 47

- 6.6.30 Instantaneous Current (I) – Page 16, Address 2

- 6.6.31 Instantaneous Voltage (V) – Page 16, Address 3

- 6.6.32 Instantaneous Active Power (P) – Page 16, Address 4

- 6.6.33 Active Power (PAVG) – Page 16, Address 5

- 6.6.34 RMS Current (IRMS ) – Page 16, Address 6

- 6.6.35 RMS Voltage (VRMS ) – Page 16, Address 7

- 6.6.36 Reactive Power (QAvg ) – Page 16, Address 14

- 6.6.37 Instantaneous Quadrature Power (Q) – Page 16, Address 15

- 6.6.38 Peak Current (IPEAK) – Page 0, Address 37

- 6.6.39 Peak Voltage (VPEAK) – Page 0, Address 36

- 6.6.40 Apparent Power (S) – Page 16, Address 20

- 6.6.41 Power Factor (PF) – Page 16, Address 21

- 6.6.42 Temperature (T) – Page 16, Address 27

- 6.6.43 Total Active Power (PSUM ) – Page 16, Address 29

- 6.6.44 Total Apparent Power (SSUM ) – Page 16, Address 30

- 6.6.45 Total Reactive Power (QSUM ) – Page 16, Address 31

- 6.6.46 DC Offset for Current (IDCOFF ) – Page 16, Address 32

- 6.6.47 DC Offset for Voltage (VDCOFF ) – Page 16, Address 34

- 6.6.48 Gain for Current (IGAIN ) – Page 16, Address 33

- 6.6.49 Gain for Voltage (VGAIN ) – Page 16, Address 35

- 6.6.50 Average Active Power Offset (POFF ) – Page 16, Address 36

- 6.6.51 Average Reactive Power Offset (QOFF ) – Page 16, Address 38

- 6.6.52 AC Offset for Current (IACOFF ) – Page 16, Address 37

- 6.6.53 Temperature Gain (TGAIN ) – Page 16, Address 54

- 6.6.54 Temperature Offset (TOFF ) – Page 16, Address 55

- 6.6.55 Calibration Scale (Scale) – Page18, Address 63

- 6.6.56 Zero-crossing Number (ZXNUM) – Page 0, Address 55

- 6.6.57 V-channel Zero-crossing Threshold (VZXLEVEL) – Page 18, Address 58

- 6.6.58 I-channel Zero-crossing Threshold (IZXLEVEL) – Page 18, Address 24

- 7. System Calibration

- 8. Basic Application Circuits

- 9. Package Dimensions

- 10. Ordering Information

- 11. Environmental, Manufacturing, & Handling Information

- 12. Revision History