2 pulse width, Figure 11. sag, swell, & overcurrent detect, Cs5490 – Cirrus Logic CS5490 User Manual

Page 21

CS5490

DS982F3

21

The CS5490 pulse generation block behaves as

follows:

• The pulse rate generated by full-scale (1.0 decimal)

power register is

F

OUT

= (PulseRate x 2000)/2

FREQ_RNG

• The PulseRate register value is

PulseRate = (F

OUT

x 2

FREQ_RNG

)/2000

= (18.5186 x 64)/2000

= 0.5925952

= 0x4BDA29

5.5.2 Pulse Width

The PulseWidth register defines the Active-low time of

each energy pulse:

Active-low = 250µs + (PulseWidth/64000).

By default, the PulseWidth register value is 1, and the

Active-low time of each energy pulse is 265.6µs. Note

that the pulse width should never exceed the pulse

period.

5.6 Voltage Sag, Voltage Swell, and

Overcurrent Detection

Voltage sag detection is used to determine when the

voltage falls below a predetermined level for a specified

interval of time (duration). Voltage swell and overcurrent

detection determine when the voltage or current rises

above a predetermined level for the duration.

The duration is set by the value in the VSag

DUR

,

VSwell

DUR

, and IOver

DUR

registers. Setting any of

these to zero (default) disables the detect feature for the

given channel. The value is in output word rate (OWR)

samples. The predetermined level is set by the values

in the VSag

LEVEL

, VSwell

LEVEL

, and IOver

LEVEL

registers.

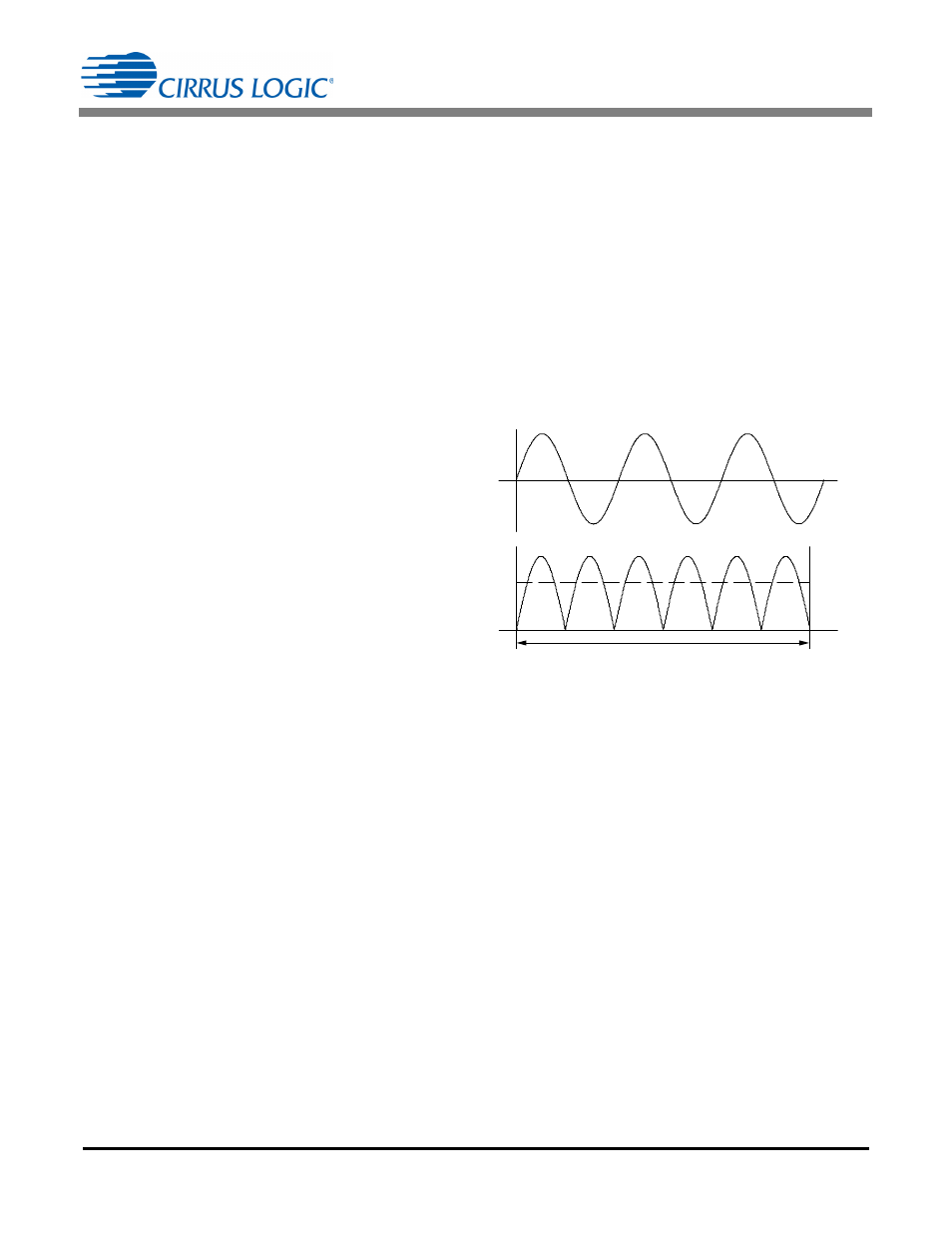

For each enabled input channel, the measured value is

rectified and compared to the associated level register.

Over the duration window, the number of samples above

and below the level are counted. If the number of

samples below the level exceeds the number of samples

above, a Status0 register bit VSAG is set, indicating a

sag condition. If the number of samples above the level

exceeds the number of samples below, a Status0

register bit VSWELL or IOVER is set, indicating a swell

or overcurrent condition (see

L e v e l

D u ra tio n

Figure 11. Sag, Swell, & Overcurrent Detect