6 high-pass & phase matching filters, 7 digital integrators, 8 low-rate calculations – Cirrus Logic CS5490 User Manual

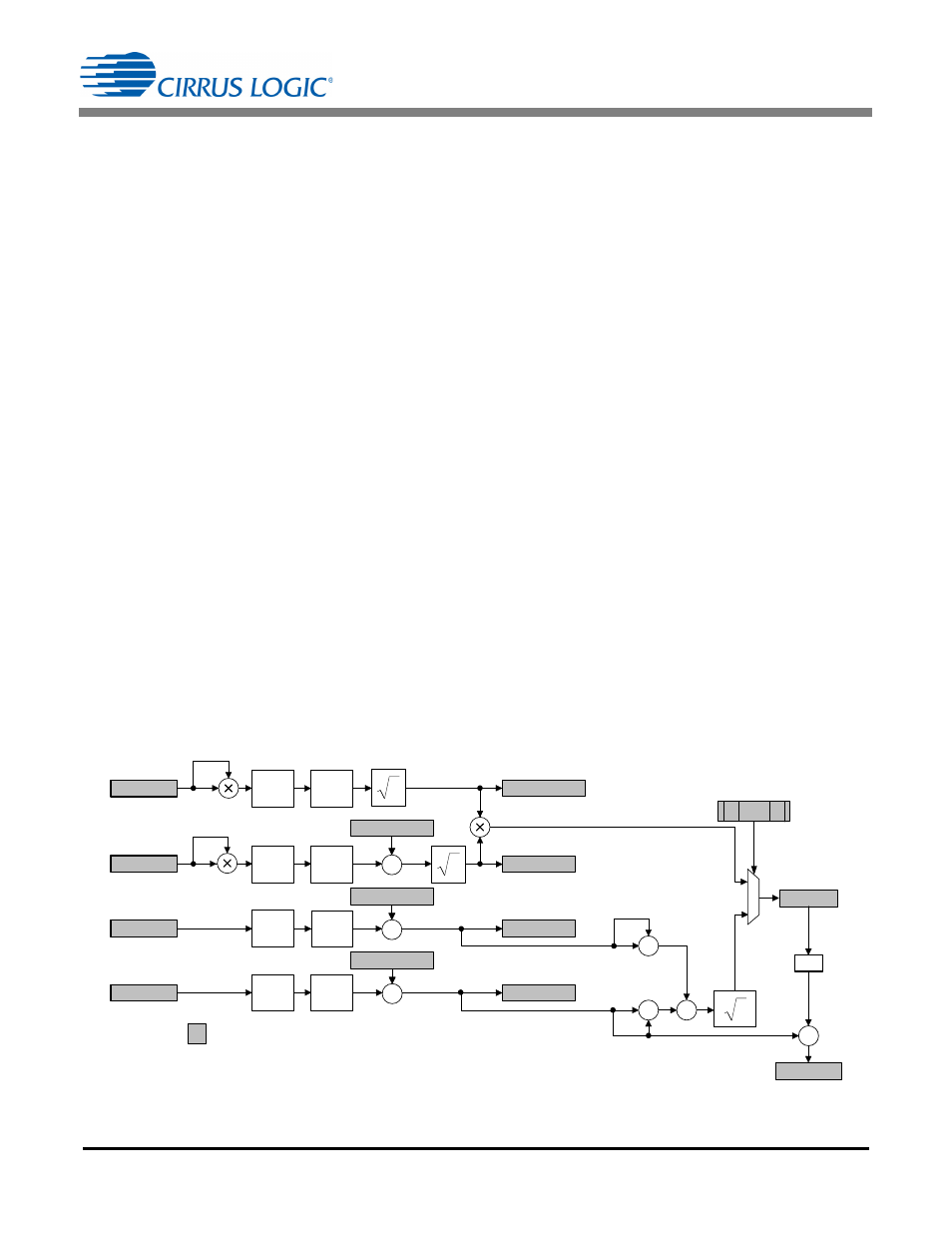

Page 16: Figure 7. low-rate calculations, 1 fixed number of samples averaging, 2 line-cycle synchronized averaging, Cs5490

CS5490

16

DS982F3

4.6 High-pass & Phase Matching Filters

Optional high-pass filters (HPF in

) remove any

DC component from the selected signal paths. Each

power calculation contains a current and voltage

channel. If an HPF is enabled in only one channel, a

phase-matching filter (PMF) should be applied to the

other channel to match the phase response of the HPF.

For AC power measurement, high-pass filters should be

enabled on the voltage and current channels. For

information about how to enable and disable the HPF or

PMF on each channel, refer to Config2 register

descriptions in section

4.7 Digital Integrators

Optional digital integrators (INT in

) are

implemented on the current channel to compensate for

the 90° phase shift and 20dB/decade gain generated

by the Rogowski coil current sensor. When a Rogowski

coil is used as the current sensor, the integrator (INT)

should be enabled on that current channel. For

information about how to enable and disable the INT on

the current channel, refer to Config2 register

descriptions in section

4.8 Low-rate Calculations

All the RMS and power results come from low-rate cal-

culations by averaging the output word rate (OWR) in-

stantaneous values over N samples, where N is the

value stored in the SampleCount register. The low-rate

interval or averaging period is N divided by OWR

(4000Hz if MCLK = 4.096MHz). The CS5490 provides

two averaging modes for low-rate calculations: Fixed

Number of Sample Averaging mode and Line-cycle

Synchronized Averaging mode. By default, the CS5490

averages with the Fixed Number of Samples Averaging

mode. By setting the AVG_MODE bit in the Config2 reg-

ister, the CS5490 will use the Line-cycle Synchronized

Averaging mode.

4.8.1 Fixed Number of Samples Averaging

N is the preset value in the SampleCount register and

should not be set less than 100. By default, the

SampleCount register is 4000. With

MCLK = 4.096 MHz, the averaging period is fixed at

N/4000 = 1 second, regardless of the line frequency.

4.8.2 Line-cycle Synchronized Averaging

When operating in Line-cycle Synchronized Averaging

mode, and when line frequency measurement is

enabled (see section

5.4 Line Frequency Measurement

on page 19), the CS5490 uses the voltage (V) channel

zero crossings and measured line frequency to

automatically adjust N such that the averaging period

will be equal to the number of half line-cycles in the

CycleCount register. For example, if the line frequency

is 51Hz, and the CycleCount register is set to 100, N will

be 4000

(100/2)/51 = 3921 during continuous

conversion. N is self-adjusted according to the line

frequency, therefore the averaging period is always

close to the whole number of half line-cycles, and the

low-rate calculation results will minimize ripple and

maximize resolution, especially when the line frequency

varies. Before starting a low-rate conversion in the

Line-cycle Synchronized Averaging mode, the

N

÷

N

N

÷

N

N

÷

N

N

÷

N

Registers

MU

X

...

...

APCM

Config 2

V

I

P

Q

I

ACOFF

S

PF

X

I

RMS

V

RMS

Q

AVG

P

AVG

-

+

Q

OFF

+

+

P

OFF

+

+

X

X

+

+

Inverse

Figure 7. Low-rate Calculations