Cs5490 – Cirrus Logic CS5490 User Manual

Page 35

CS5490

DS982F3

35

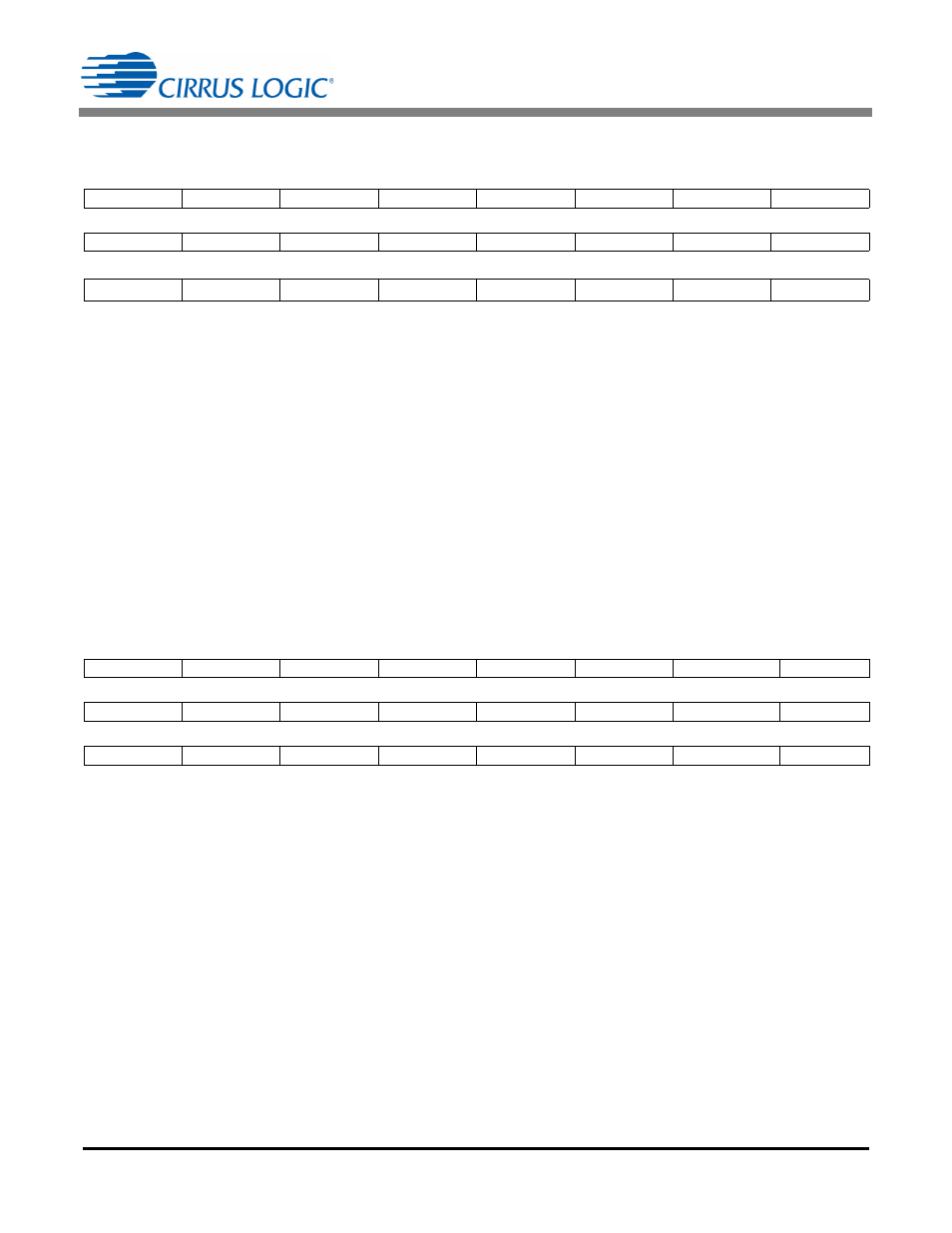

6.6.4 Phase Compensation (PC) – Page 0, Address 5

Default = 0x00 0000

[23:22]

Reserved.

CPCC[1:0]

Coarse phase compensation control for I & V.

00 = No extra delay

01 = 1 OWR delay in current channel

10 = 1 OWR delay in voltage channel

11 = 2 OWR delay in voltage channel

[19:9]

Reserved.

FPCC[8:0]

Fine phase compensation control for I & V.

Sets a delay in current, relative to voltage.

Resolution: 0.008789° at 50Hz and 0.010547° at 60Hz (OWR = 4000)

6.6.5 UART Control (SerialCtrl)

–

Page 0, Address 7

Default = 0x02 004D

[23:19]

Reserved.

RX_PU_OFF

Disable the pull-up resistor on the RX input pin.

0 = Pull-up resistor enabled (Default)

1 = Pull-up resistor disabled

RX_CSUM_OFF Disable the checksum on serial port data.

0 = Enable checksum

1 = Disable checksum (Default)

[16]

Reserved.

BR[15:0]

Baud rate (serial bit rate).

BR[15:0] = Baud Rate x 524288 / MCLK

23

22

21

20

19

18

17

16

-

-

CPCC[1]

CPCC[0]

-

-

-

-

15

14

13

12

11

10

9

8

-

-

-

-

-

-

-

FPCC[8]

7

6

5

4

3

2

1

0

FPCC[7]

FPCC[6]

FPCC[5]

FPCC[4]

FPCC[3]

FPCC[2]

FPCC[1]

FPCC[0]

23

22

21

20

19

18

17

16

-

-

-

-

-

RX_PU_OFF RX_CSUM_OFF

-

15

14

13

12

11

10

9

8

BR[15]

BR[14]

BR[13]

BR[12]

BR[11]

BR[10]

BR[9]

BR[8]

7

6

5

4

3

2

1

0

BR[7]

BR[6]

BR[5]

BR[4]

BR[3]

BR[2]

BR[1]

BR[0]