Spw-10x spacewire router – Atmel SpaceWire Router SpW-10X User Manual

Page 110

Ref.: UoD_SpW-10X_

UserManual

Issue: 3.4

SpW-10X

SpaceWire Router

User Manual

Date: 11

th

July 2008

Preliminary

110

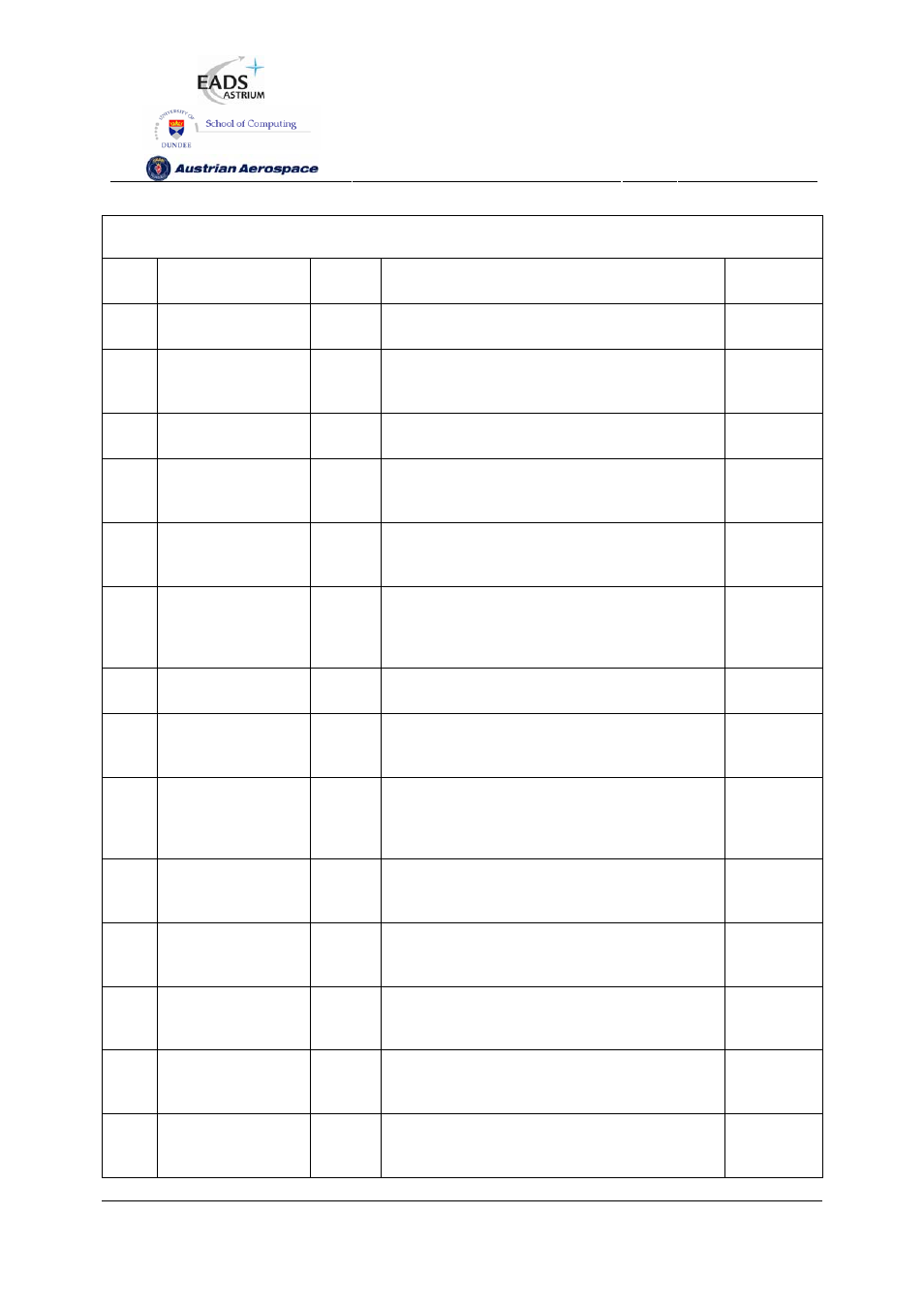

Table 9-5 Configuration Port Control/Status Register Fields

Bits Name

Reset

Value

Description Read/Write

0

Error active

‘0’

The error active bit is set when one of the error

bits is active

R

1

Port timeout error

‘0’

The port timeout error bit is set when a timeout

event is detected by the configuration port

routing logic.

R

2 Invalid

Header

CRC

‘0’

The Invalid header CRC bit is set when the

header CRC is invalid.

R

3

Invalid Data CRC

‘0’

The invalid data CRC is set when the data part

of the packet is corrupted and the CRC does

not match the internally generated CRC.

R

4 Invalid

Destination

Key

‘0’

The invalid destination key bit is set when the

destination key in the command packet is

invalid.

R

5 Command

not

implemented

‘0’

The command not implemented bit is set when

the command code is a valid RMAP code but

the command is not supported by the

SpaceWire Router.

R

6

Invalid Data Length ‘0’

The invalid data length bit is set when a data

length error is detected

R

7 Invalid

RMW

Data

Length

‘0’

The read modify write command data length is

invalid. When a read modify write is performed

the expected data length is 8.

R

8 Invalid

Destination

Logical Address

‘0’

The invalid destination logical address bit is set

when the destination logical address in the

command packet is not the default value of

254.

R

9

Early EOP

‘0’

The early EOP bit is set when the command

packet is terminated before the end of packet

with an EOP

R

10

Late EOP

‘0’

The late EOP bit is set when the command

packet is not terminated correctly and trailing

bytes are detected before the end of packet.

R

11

Early EEP

‘0’

The early EEP bit is set when the command

packet is terminated before the end of packet

with an EEP

R

12

Late EEP

‘0’

The late EEP bit is set when the command

packet is not terminated correctly and trailing

bytes are detected before the end of packet.

R

13 Verify

Buffer

Overrun Error

‘0’

The verify buffer overrun error bit is set when a

verified write command is performed and the

data length is not 4.

R