NORD Drivesystems BU0090 User Manual

Page 27

3 Bus structure and topology

BU 0090 GB

27

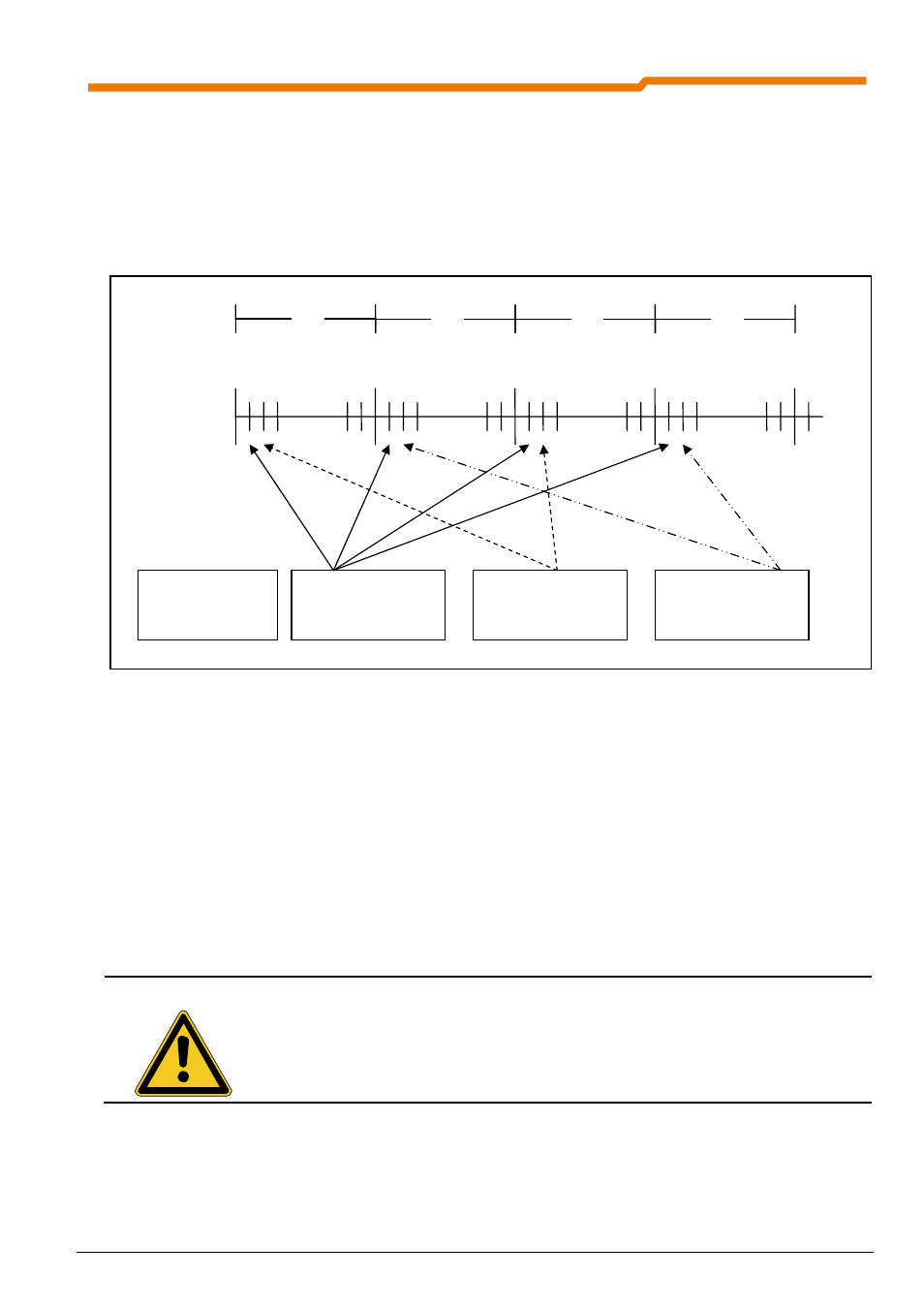

An additional bit is required in order to address an A/B slave. This bit is inserted into the reference data area,

so that the content of the 4 data bits must be divided over 2 protocols, i.e. 2 transmission cycles.

On the other hand, the response telegrams contain all 4 data bits, so that the telegrams from the slave to the

master are completely updated after each order.

Also, due to the extended address range, A/B slaves can only be accessed every 2nd cycle. This also

additionally doubles the cycle time for these participants.

For the operation and parameterisation of the master please refer to the particular manual of the AS-i master

manufacturer. There you can find more detailed information regarding the individual AS interface masters

used.

The main component of the AS interface is a special slave module, which can control the following functions:

I. only 4 inputs,

II. only 4 outputs

III. 4 inputs and 4 outputs simultaneously (within a single telegram)

Therefore, according to III, there are a maximum of 248 binary inputs and outputs for an AS interface system

with 31 slaves (496 in extended address mode with A/B slaves). This AS interface chip (ASIC) has 4

parameter bits for the non-cyclic setting of special slaves. If the parameter bits are used, the master transmits

asynchronous parameter telegrams between the normal data cycles.

NOTE

The address range available is from 0 - 31 (62 for A/B slaves):

For normal addressing of slaves do not use the address 0. Address 0 is an exception and is

reserved for automatic addressing via the master.

In general, there are two categories of AS interface slaves:

Integrated

slaves

Slave modules for the connection of conventional (no field bus capability) sensors, actuators or field

devices

Participants

1 2 3a 4 … 30a 31 1 2 3b 4 … 30b 31 1 2 3a 4 … 30a 31 1 2 3b 4 … 30b 31 1 2

5ms

Slave 2

(Standard Slave)

Transmit 4DB

Receive 4DB

Cyclical data transfer

from master

Slave 3a

(A/B Slave)

Transmit

2

DB

Receive 4DB

Slave 3b

(A/B Slave)

Transmit

2

DB

Receive 4DB

5ms

5ms

5ms

Cycle time