GW Instek GDS-800 Series Programming Manual User Manual

Page 77

GDS-806/810/820/840 Programming Manual

76

Status Registers.

There are two status registers are included with this oscilloscope which defined by

IEEE-488.1 and IEEE-488.2 standards.

z

Status Byte Register (SBR)

z

Standard Event Status Register (SESR)

Status Byte Register (SBR): The SBR (Table 5-3) summaries the status of all other

registers and queue.

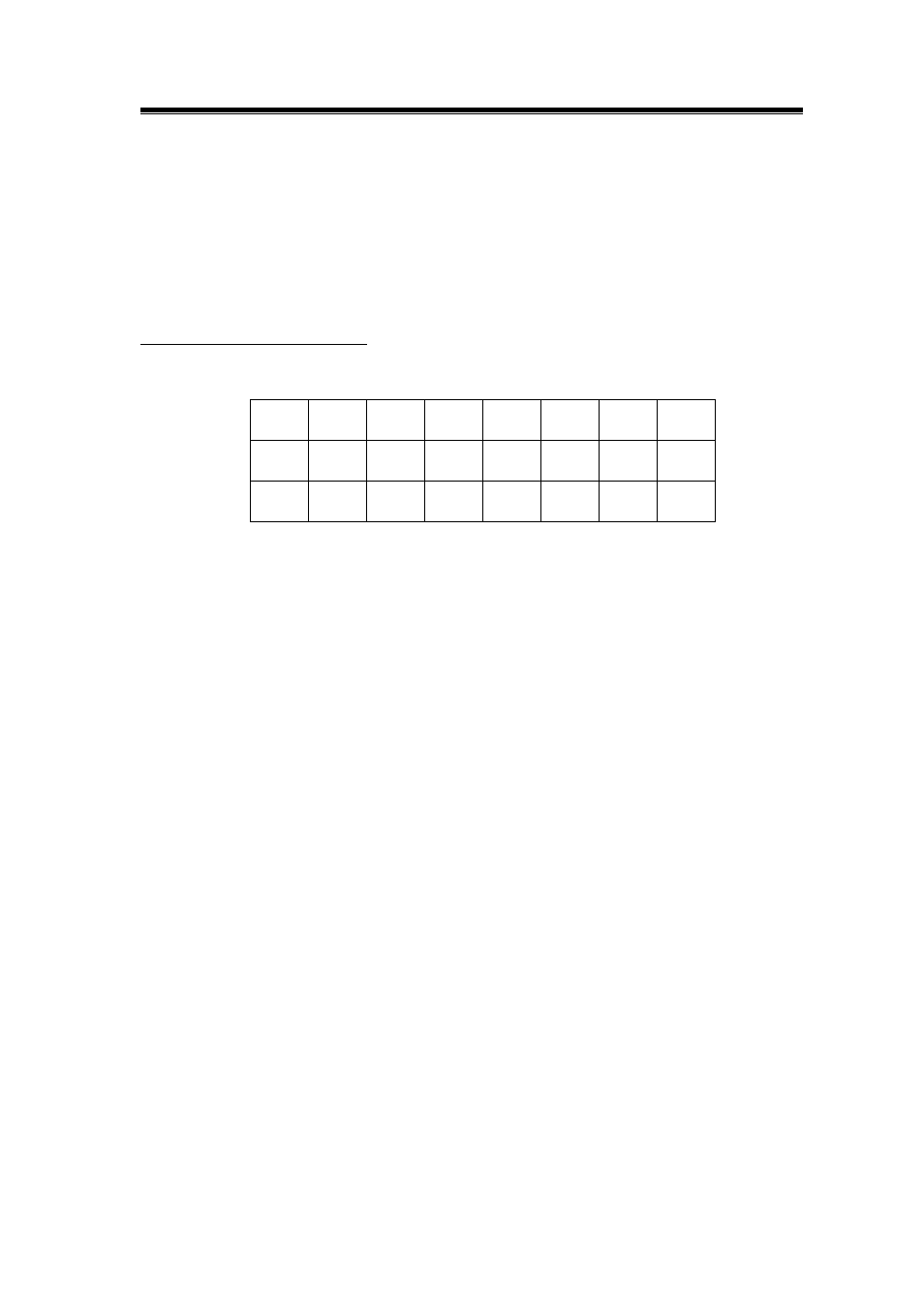

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

OPER RQS

ESB

MAV QUES

NU

NU

NU

128

64

32

16

8

4

2

1

Table 5-3: Status Byte Register (SBR)

From the bit 0 to bit 2 are not used, these bits are always zero.

The bit 3 (QUES, QUEStionable) is the summary bit for the QESR (QUEStionable

Event Status Register). When this bit is high it indicates that status is enabled and

present in the QESR.

The bit 4 (MAV, Message Available) indicates that output is available in the output

queue.

The bit 5 (ESB, Event Status Bit) is the summary bit for the Standard Event Status

Register (SESR). When this bit is high it indicates that status is enabled and

present in the SESR.

The bit 6 (RQS, Request Service) is obtained from a serial poll. This bit shows that

this oscilloscope requests service from the GPIB controller.

The bit 7 (OPER, OPERation) is the summary bit for the OESR (OPERation EVENt

STATus Register).