Product outline – GW Instek SFG-830 User Manual User Manual

Page 7

p. 4 SFG-830

2. Product Outline

The frequency synthesis method applied by SFG-830 is Direct Digital Synthesis

(DDS), a new technique that generates stable output frequency with extraordinary

resolution.

Unlike SFG-830, traditional frequency synthesized function generators typically use

Phase Locked Loop (PLL) techniques. In order to synthesize frequencies, PLL should

be high-resolution (up to 1:10

6

in general) and needs a stable frequency to be

reference. Due to the utilization of dynamic loop filter, problems such as poor phase

jitter and frequency switching response may occur when running the PLL system.

As in generating waveforms, PLL needs a wave-shaping circuit with an address

counter that controlled by a variable frequency clock. The counter addresses

memory locations in a waveform RAM, and the RAM output is converted by a high

speed digital-to-analog converter (DAC) to produce an analog output signal. Problems

like poor phase jitter and transient response may arise here as well.

Although DDS also generates analogue waveforms by way of the waveform RAM and

high speed DAC, it does not have the problems as PLL does due to the use of fixed

frequency clock (fs). Besides, the resolution of DDS is higher than that of PLL’s.

DDS’s resolution is fs/2

k

where the digit of the control frequency word (K), which is

more than 32bits in general, decides the quality of it.

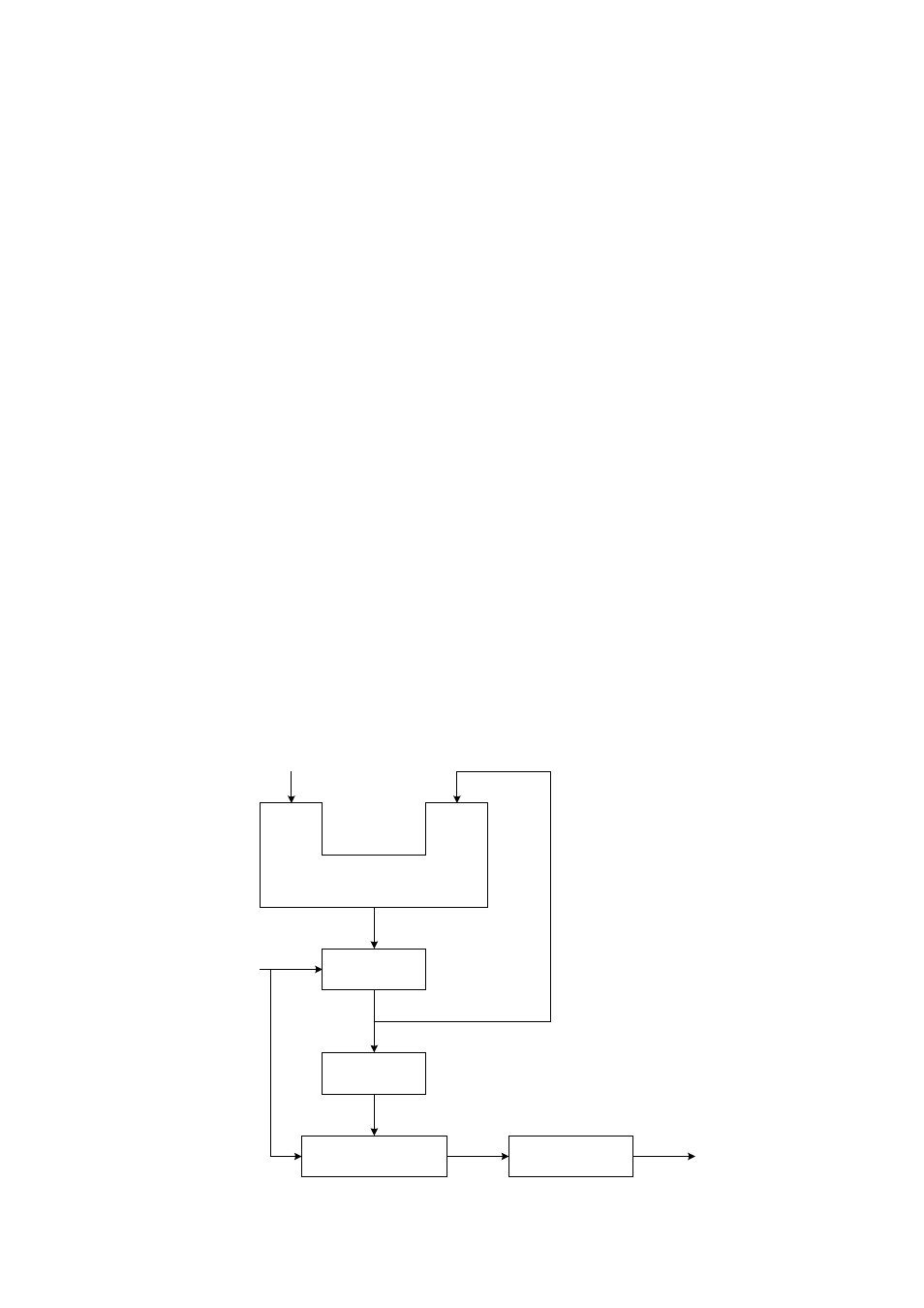

Graph1 indicates the fundamental construction of a DDS frequency synthesizer.

System

Clock

Register

ROM or RAM

Accumulator

Digital / Analog

Converter

Lowpass Filter

32

32

32

24

12

fs

fo

K

(Frequency Control Word)