Agilent Technologies E8267D PSG User Manual

Page 256

242

Chapter 12

Peripheral Devices

N5102A Digital Signal Interface Module

Parallel and Parallel Interleaved Port Configuration Clock Rates

Parallel and parallel interleaved port configurations have other limiting factors for the clock and

sample rates:

•

logic type

•

Clocks per sample selection

•

IQ or IF digital signal type

Clocks per sample (clocks/sample) is the ratio of the clock to sample rate. For an IQ signal type, the

sample rate is reduced by the clocks per sample value when the value is greater than one. For an IF

signal or an input signal, clocks per sample is always set to one. Refer to

for the Output

mode parallel and parallel interleaved port configuration clock rates.

For Input mode, the maximum clock rate is limited by the following factors:

•

sample size

•

data type

•

selected filter for Pre- FIR Samples

Refer to

for the Input mode parallel and parallel interleaved port configuration clock

rates.

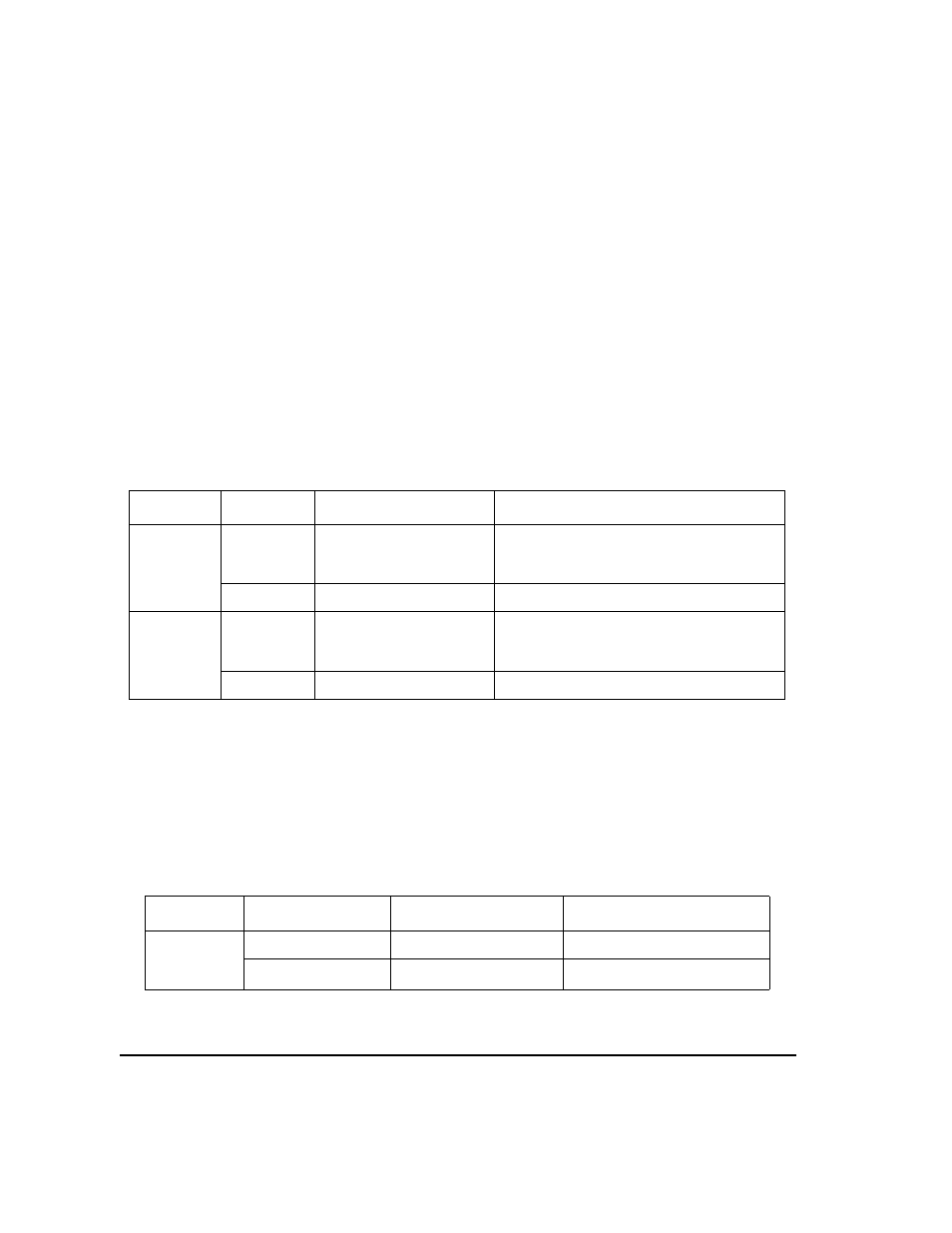

Table 12-5 Output Parallel and Parallel Interleaved Clock Rates

Logic Type

Signal Type

Minimum Rate

Maximum Rate

LVDS

IQ

1 x (clocks/sample) kHz

the smaller of: 100 x (clocks /sample) MHz

or

400 MHz

IF

4 kHz

400 MHz

Other

IQ

1 x (clocks/sample) kHz

the smaller of: 100 x (clocks /sample) MHz

or

150 MHz

IF

4 kHz

150 MHz

Table 12-6 Input Parallel and Parallel Interleaved Clock Rates

Logic Type

Data Type

Minimum Rate

Maximum Rate

N/A

Samples

1 kHz

100 MHz

Pre- FIR Samples

1 kHz

50

a

MHz

a.The maximum sample rate depends on the selected filter when the data rate is Pre-FIR Samples. Refer to

for more information.