Agilent Technologies E8267D PSG User Manual

Page 260

246

Chapter 12

Peripheral Devices

N5102A Digital Signal Interface Module

Clock Timing for Parallel Data

Some components require multiple clocks during a single sample period. (A sample period consists of

an I and Q sample). For parallel data transmissions, you can select one, two, or four clocks per

sample. For clocks per sample greater than one, the I and Q samples are held constant to

accommodate the additional clock periods. This reduces the sample rate relative to the clock rate by

a factor equal to the clocks per sample selection. For example, when four is selected, the sample rate

is reduced by a factor of four (sample rate to clock rate ratio).

demonstrates the clock

timing for each clocks per sample selection. For input mode, the clocks per sample setting is always

one.

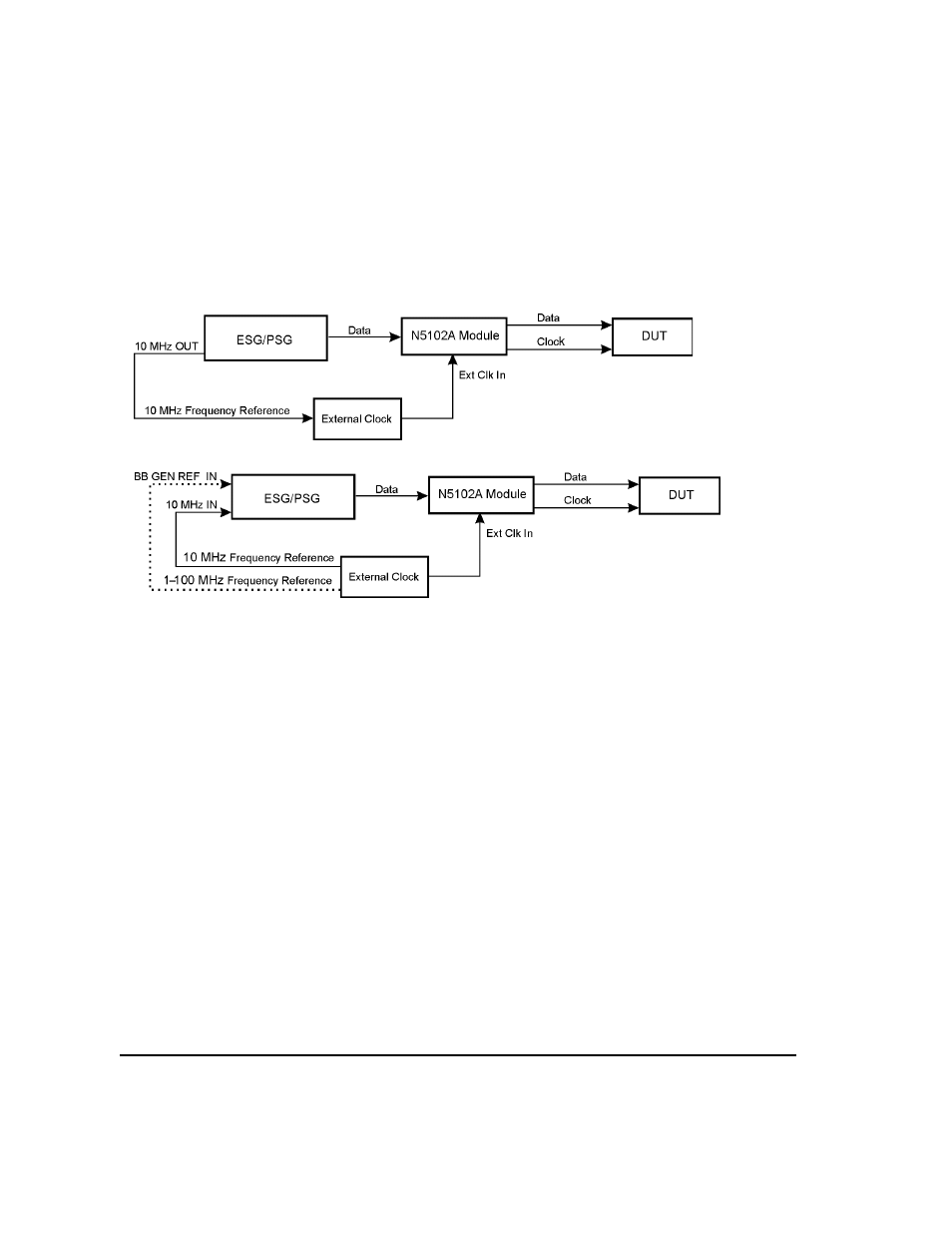

Externally Supplied Clock

NOTE: Use only one of the two signal generator frequency reference inputs.