Rainbow Electronics DS2182A User Manual

Page 10

DS2182A

041995 10/22

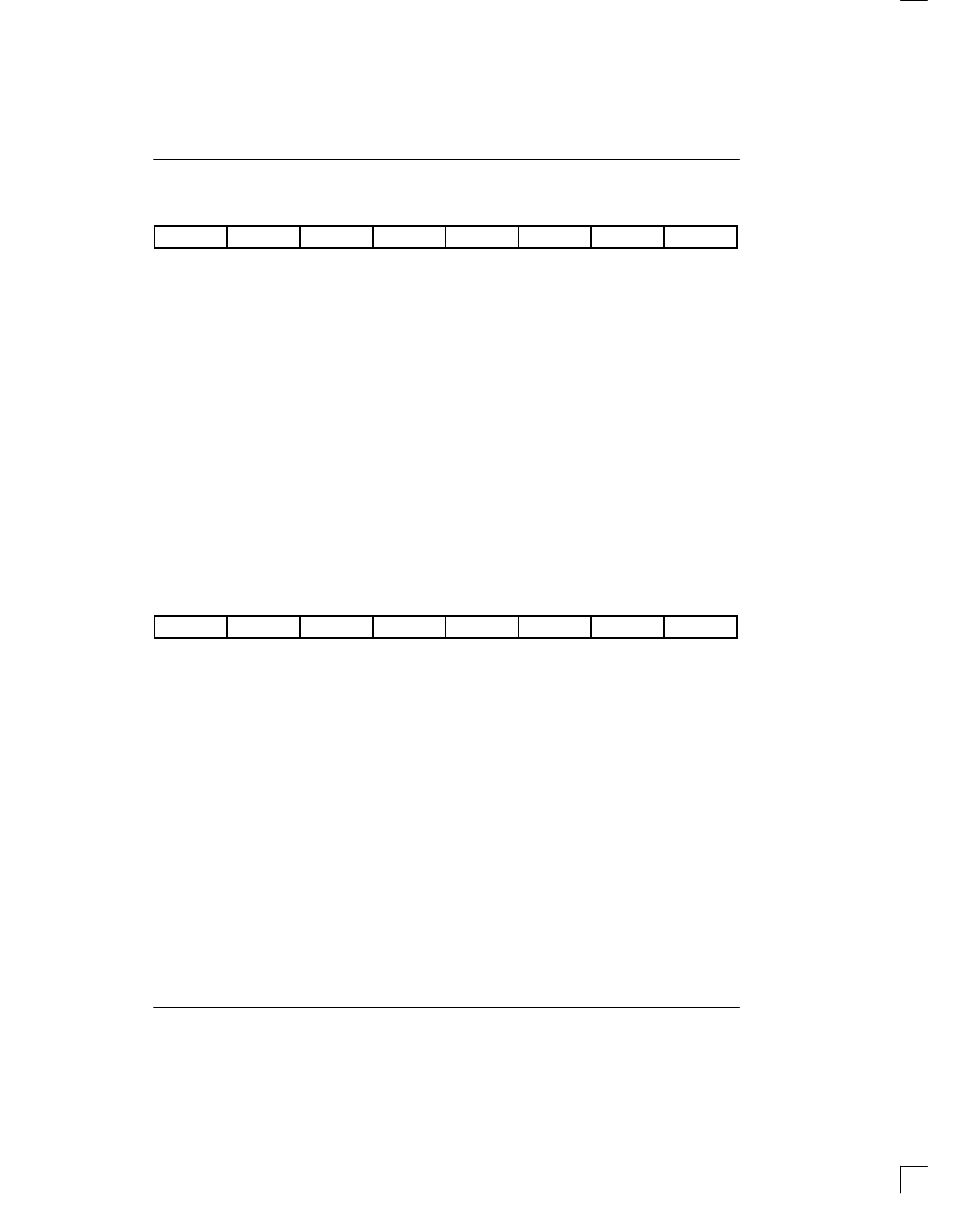

RSR2: RECEIVE STATUS REGISTER 2 Figure 10

(MSB)

(LSB)

SEFE

RCLC

RBLC

FERR

FECS

OOFCS

CRCCS

BPVCS

SYMBOL

POSITION

NAME AND DESCRIPTION

SEFE

RSR2.7

Severely Errored Framing Event. Set when 2 out of 6 framing bits (Ft or

FPS) are received in error.

RCLC

RSR2.6

Receive Carrier Loss Clear. Set when the carrier signal is restored; will

remain set until read.

RBLC

RSR2.5

Receive Blue Alarm Clear. Set when the Blue Alarm (AIS) is no longer de-

tected; will remain set until read.

FERR

RSR2.4

Frame Bit Error. Set when FT (193S) or FPS (193E) bit errors occur.

FECS

RSR2.3

Frame Error Count Saturation. Set on the next frame error event after

the 8-bit Frame Error Count Register (FECR) saturates at 255.

OOFCS

RSR2.2

Out Of Frame Count Saturation. Set on the next OOF event after the

8-bit OOF Count Register (OOFCR) saturates at 255.

CRCCS

RSR2.1

CRC Count Saturation. Set on the next CRC error event after the 8-bit

CRC Count Register (CRCCR) saturates at 255.

BPVCS

RSR2.0

Bipolar Violation Count Saturation. Set on the next BPV error event af-

ter the 16-bit Bipolar Violation Count Register (BVCR) saturates at 65,535.

RIMR2: RECEIVE INTERRUPT MASK REGISTER 2 Figure 11

(MSB)

(LSB)

SEFE

RCLC

RBLC

FERR

FECS

OOFCS

CRCCS

BPVCS

SYMBOL

POSITION

NAME AND DESCRIPTION

SEFE

RIMR2.7

Severely Errored Framing Event Mask.

0 = interrupt masked

1 = interrupt enabled

RCLC

RIMR2.6

Receive Carrier Loss Clear Mask.

0 = interrupt masked

1 = interrupt enabled

RBLC

RIMR2.5

Receive Blue Alarm Clear Mask.

0 = interrupt masked

1 = interrupt enabled

FERR

RIMR2.4

Frame Bit Error Mask.

1 = interrupt enabled

0 = interrupt masked

FECS

RIMR2.3

Frame Error Count Saturation Mask.

1 = interrupt enabled

0 = interrupt masked

OOFCS

RIMR2.2

Out Of Frame Count Saturation Mask.

1 = interrupt enabled

0 = interrupt masked