13 registers – Rainbow Electronics T89C51CC01 User Manual

Page 86

86

T89C51CC01

Rev. D – 17-Dec-01

15.13 Registers

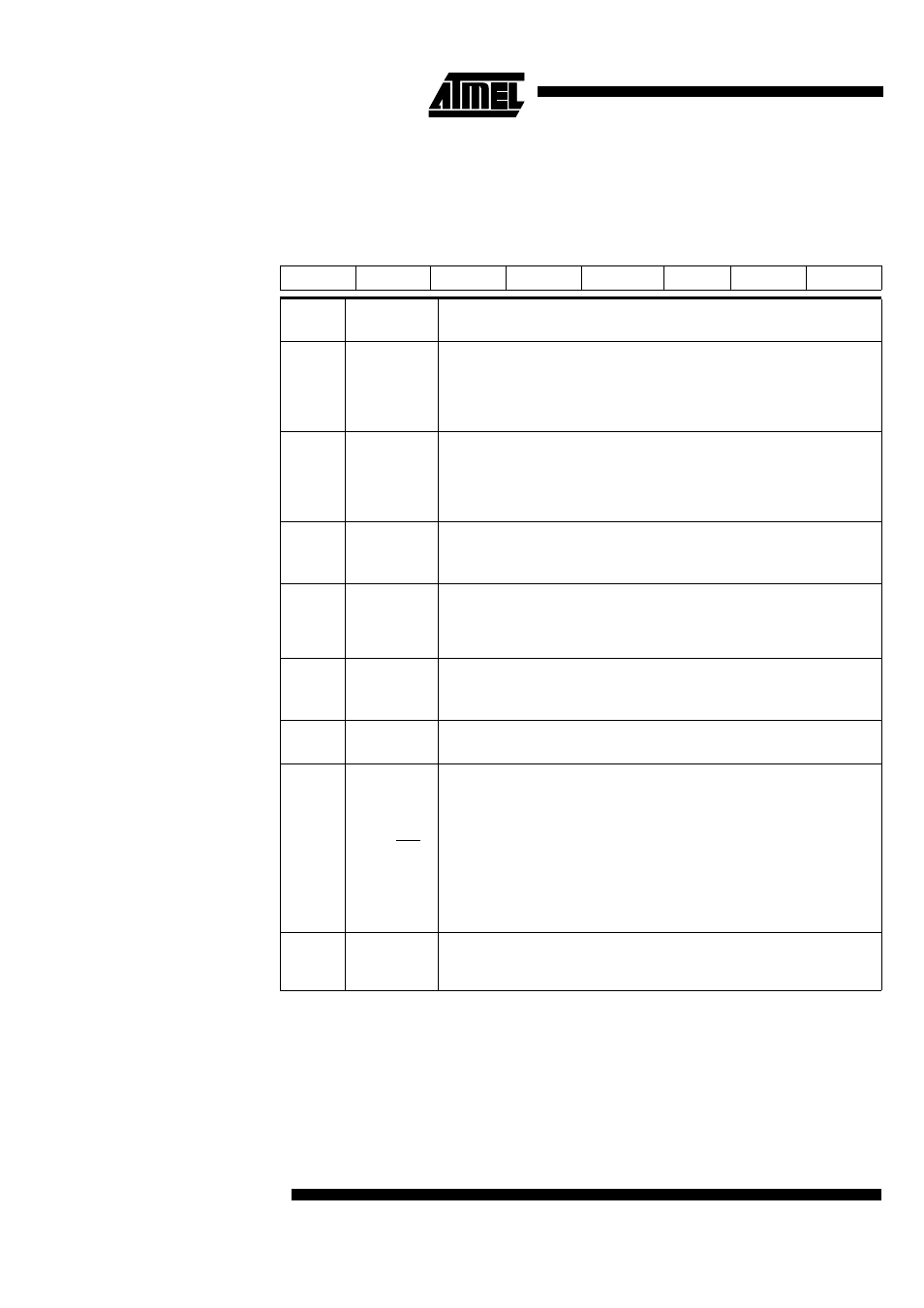

Table 38. CANGCON Register

CANGCON (S:ABh)

CAN General Control Register

Reset Value: 0000 0x00b

7

6

5

4

3

2

1

0

ABRQ

OVRQ

TTC

SYNCTTC

AUTOBAUD

TEST

ENA

GRES

Bit

Number

Bit Mnemonic

Description

7

ABRQ

Abort request

Not an auto-resetable bit. A reset of the ENCH bit (message object control &

DLC register) is done for each message object. The pending transmission

communications are immediately aborted but the on-going communication will

be terminated normally, setting the appropriate status flags, TXOK or RXOK.

6

OVRQ

Overload frame request (initiator).

Auto-resetable bit.

Set to send an overload frame after the next received message.

Cleared by the hardware at the beginning of transmission of the overload

frame.

5

TTC

Network in Timer Trigger communication

set to select node in TTC.

clear to disable TTC features.

4

SYNCTTC

Synchronization of TTC

When this bit is set the TTC timer is caught on the last bit of the End Of Frame.

When this bit is clear the TTC timer is caught on the Start Of Frame.

This bit is only used in the TTC mode.

3

AUTOBAUD

AUTOBAUD

set to active listening mode.

Clear to disable listening mode

2

TEST

Test mode. The test mode is intended for factory testing and not for customer

use.

1

ENA/STB

Enable/Standby CAN controller

When this bit is set, it enables the CAN controller and its input clock.

When this bit is clear, the on-going communication is terminated normally and

the CAN controller state of the machine is frozen (the ENCH bit of each

message object does not change).

In the standby mode, the transmitter constantly provides a recessive level; the

receiver is not activated and the input clock is stopped in the CAN controller.

During the disable mode, the registers and the mailbox remain accessible.

Note that two clock periods are needed to start the CAN controller state of the

machine.

0

GRES

General reset (software reset).

Auto-resetable bit. This reset command is ‘ORed’ with the hardware reset in

order to reset the controller. After a reset, the controller is disabled.