3 dual data pointer, Figure 5), Figure 6 – Rainbow Electronics T89C51CC01 User Manual

Page 24

24

T89C51CC01

Rev. D – 17-Dec-01

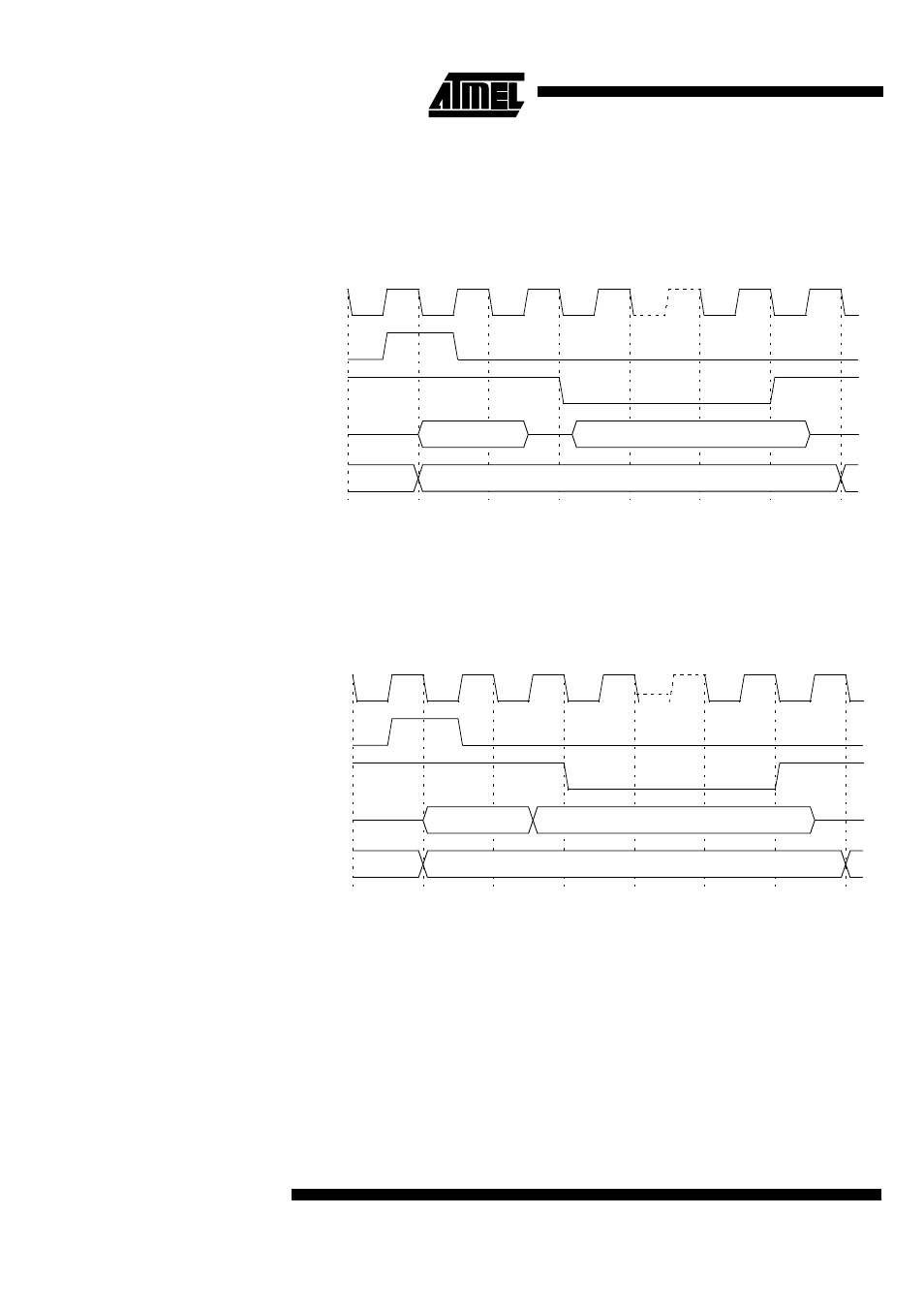

For simplicity, the accompanying figures depict the bus cycle waveforms in idealized

form and do not provide precise timing information. For bus cycle timing parameters

refer to the Section “AC Characteristics” of the T89C51CC01 datasheet.

Figure 5. External Data Read Waveforms

Notes:

1. RD# signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

Figure 6. External Data Write Waveforms

Notes:

1. WR# signal may be stretched using M0 bit in AUXR register.

2. When executing MOVX @Ri instruction, P2 outputs SFR content.

7.3 Dual Data Pointer

7.3.1 Description

The T89C51CC01 implements a second data pointer for speeding up code execution

and reducing code size in case of intensive usage of external memory accesses.

DPTR0 and DPTR1 are seen by the CPU as DPTR and are accessed using the SFR

addresses 83h and 84h that are the DPH and DPL addresses. The DPS bit in AUXR1

register (see Figure 5) is used to select whether DPTR is the data pointer 0 or the data

pointer 1 (see Figure 7).

ALE

P0

P2

RD#1

DPL or Ri

D7:0

DPH or P22

P2

CPU Clock

ALE

P0

P2

WR#1

DPL or Ri

D7:0

P2

CPU Clock

DPH or P22