Rainbow Electronics T89C51CC01 User Manual

Page 34

34

T89C51CC01

Rev. D – 17-Dec-01

9.2.1 FM0 Memory

Architecture

The flash memory is made up of 4 blocks (see Figure 11):

3.

The memory array (user space) 32 Kbytes

4.

The Extra Row

5.

The Hardware security bits

6.

The column latch registers

User Space

This space is composed of a 32 Kbytes FLASH memory organized in 256 pages of 128

bytes. It contains the user’s application code.

Extra Row (XRow)

This row is a part of FM0 and has a size of 128 bytes. The extra row may contain infor-

mation for boot loader usage.

Hardware security Byte

The Hardware security Byte space is a part of FM0 and has a size of 1 byte.

The 4 MSB can be read/written by software, the 4 LSB can only be read by software and

written by hardware in parallel mode.

Column latches

The column latches, also part of FM0, have a size of full page (128 bytes).

The column latches are the entrance buffers of the three previous memory locations

(user array, XROW and Hardware security byte).

9.2.2 Cross Flash Memory

Access Description

The FM0 memory can be program only from FM1. Programming FM0 from FM0 or from

external memory is impossible.

The FM1 memory can be program only by parallel programming.

The Table 8 show all software flash access allowed.

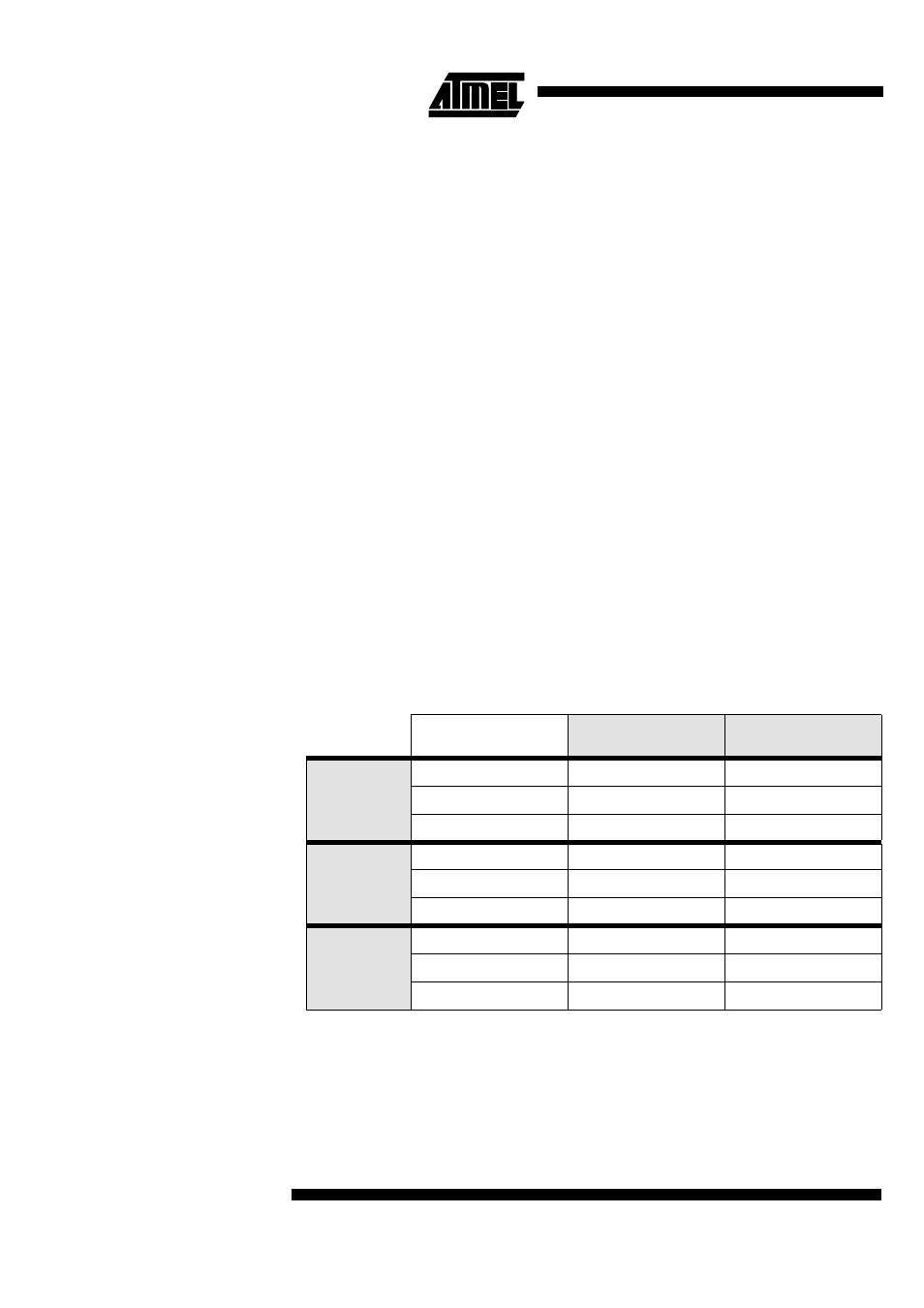

Table 8. Cross Flash Memory Access

C

o

d

e

ex

ec

ut

in

g

fr

o

m

Action

FM0

(user Flash)

FM1

(boot Flash)

FM0

(user Flash)

Read

ok

-

Load column latch

ok

-

Write

-

-

FM1

(boot flash)

Read

ok

ok

Load column latch

ok

-

Write

ok

-

External

memory

EA = 0

Read

-

-

Load column latch

-

-

Write

-

-