1 watchdog programming, 2 watchdog timer during power down mode and idle – Rainbow Electronics T89C51CC01 User Manual

Page 68

68

T89C51CC01

Rev. D – 17-Dec-01

14.1 WatchDog

Programming

The three lower bits (S0, S1, S2) located into WDTPRG register permit to program the

WDT duration.

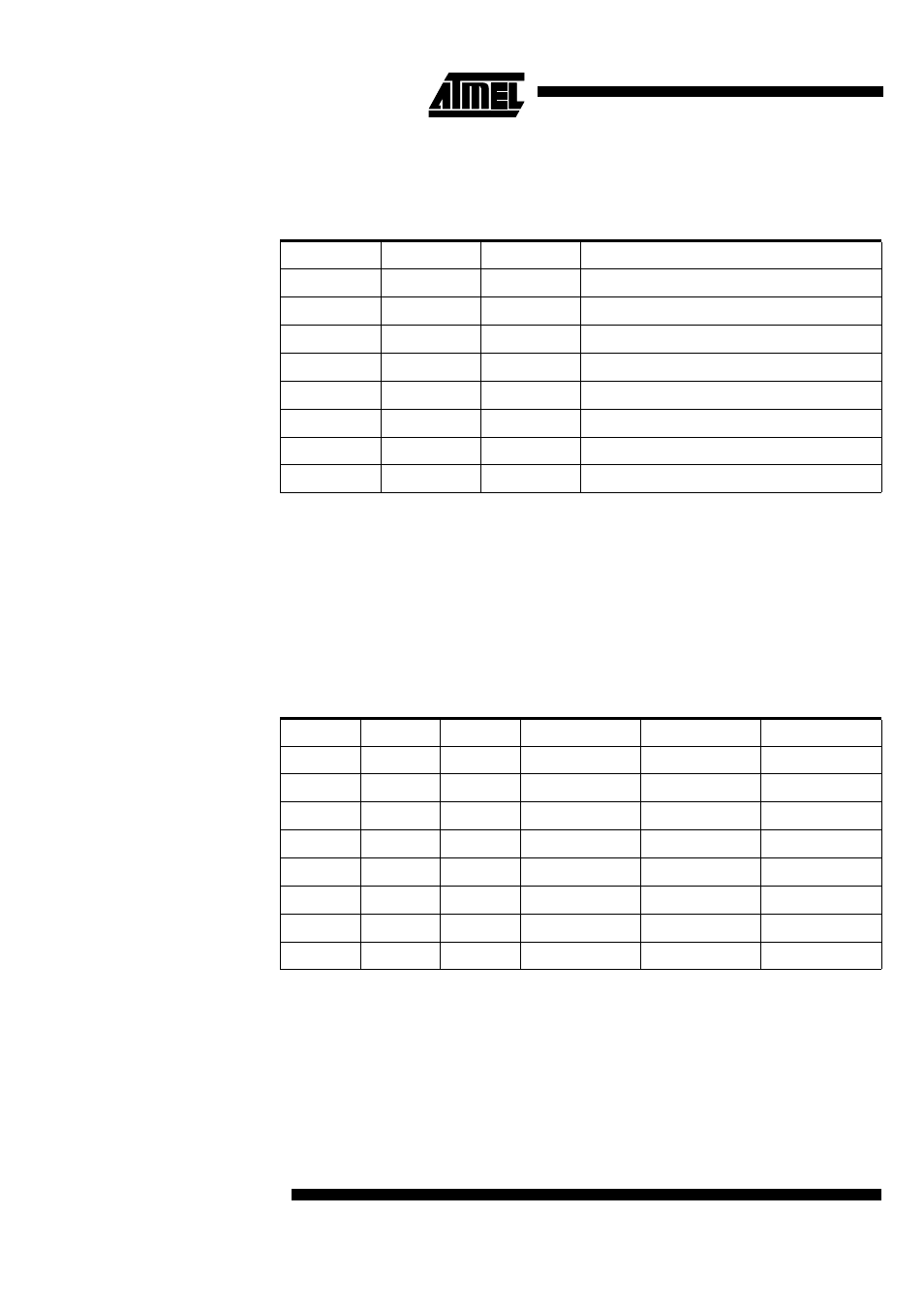

Table 32. Machine Cycle Count

To compute WD Time-Out, the following formula is applied:

Note:

Svalue represents the decimal value of (S2 S1 S0)

Find Hereafter computed Time-Out value for Fosc

XTAL

= 12MHz in X1 mode

Table 33. Time-Out Computation

14.2 WatchDog Timer

during Power down

mode and Idle

In Power Down mode the oscillator stops, which means the WDT also stops. While in

Power Down mode, the user does not need to service the WDT. There are 2 methods of

exiting Power Down mode: by a hardware reset or via a level activated external interrupt

which is enabled prior to entering Power Down mode. When Power Down is exited with

hardware reset, the watchdog is disabled. Exiting Power Down with an interrupt is signif-

icantly different. The interrupt shall be held low long enough for the oscillator to stabilize.

When the interrupt is brought high, the interrupt is serviced. To prevent the WDT from

resetting the device while the interrupt pin is held low, the WDT is not started until the

S2

S1

S0

Machine Cycle Count

0

0

0

2

14

- 1

0

0

1

2

15

- 1

0

1

0

2

16

- 1

0

1

1

2

17

- 1

1

0

0

2

18

- 1

1

0

1

2

19

- 1

1

1

0

2

20

- 1

1

1

1

2

21

- 1

S2

S1

S0

Fosc=12MHz

Fosc=16MHz

Fosc=20MHz

0

0

0

16.38 ms

12.28 ms

9.82 ms

0

0

1

32.77 ms

24.57 ms

19.66 ms

0

1

0

65.54 ms

49.14 ms

39.32 ms

0

1

1

131.07 ms

98.28 ms

78.64 ms

1

0

0

262.14 ms

196.56 ms

157.28 ms

1

0

1

524.29 ms

393.12 ms

314.56 ms

1

1

0

1.05 s

786.24 ms

629.12 ms

1

1

1

2.10 s

1.57 s

1.25 ms

FTime

Out

F

w d

12

2

14

2

Svalue

Ч

(

)

1

–

(

)

Ч

-------------------------------------------------------------------

=

–