Remote interface reference – American Magnetics 286 Multi-Sensor Liquid Level Instrument (CE-Marked) User Manual

Page 77

63

Remote Interface Reference

SCPI Status System

An enable register (or bitmask) defines which bits in an event register are

reported to the Status Byte register group. An enable register can be both

written and queried. The

*CLS

(clear status) command does not clear an

enable register. To enable or disable bits in an enable register, write a

decimal value which corresponds to the binary-weighted sum of the bits

you wish reported to the Status Byte register.

5.2.2.1 Status Byte Registers

The Status Byte register group reports conditions from the Standard

Event register or output buffers. Data in the output buffer is immediately

reported in the “Message Available” bit (bit 4). Clearing a bit in the

Standard Event or Alarm Event registers will update the corresponding

bit in the Status Byte register, according to the Standard Event and Alarm

Event enable registers. Reading the pending messages in the output

buffers will clear the “Message Available” bit. The bit definitions for the

Status Byte register are defined in Table 5-1.

Bit 4, indicating available data in an output buffer, is similar in that the

SRQ is only asserted when data is first available in an output buffer. Bit 4

remains set until all data has been read from the output buffer.

The Status Byte condition register is cleared when any of the following

occurs:

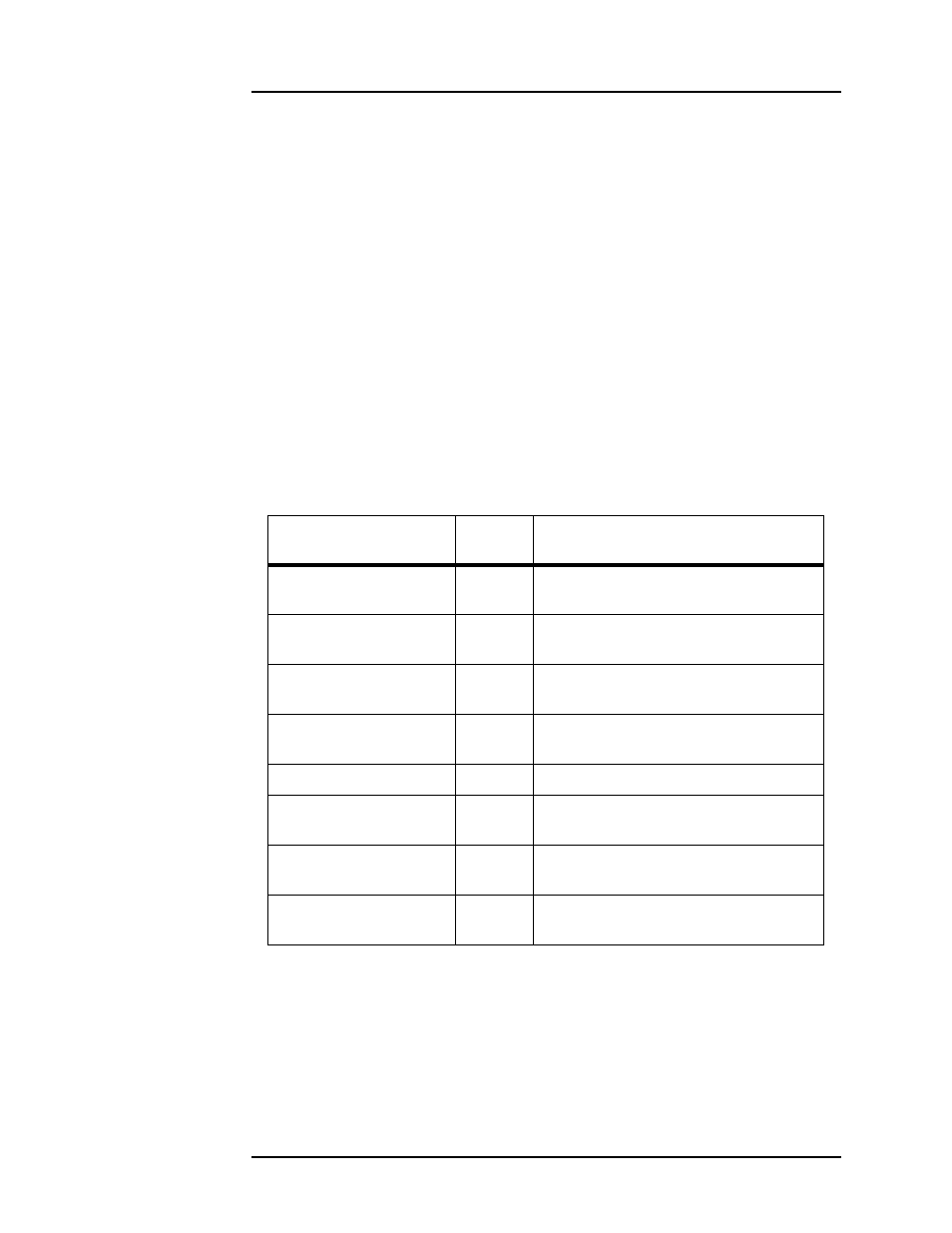

Table 5-1. Bit definitions for the Status Byte register.

Bit Number

Decimal

Value

Definition

0 CH 1 Alarm Event

1

One or more enabled bits are set in an

Alarm Event register of Channel 1.

1 CH 2 Alarm Event

2

One or more enabled bits are set in an

Alarm Event register of Channel 2.

2 CH 3 Alarm Event

4

One or more enabled bits are set in an

Alarm Event register of Channel 3.

3 CH 4 Alarm Event

8

One or more enabled bits are set in an

Alarm Event register of Channel 4.

4 Message Available

16

The output buffer contains unread data.

5 Standard Event

32

One or more enabled bits are set in the

Standard Event register.

6 Status Byte Summary

64

One or more enabled bits are set in the

Status Byte register.

7 Measurement Event

128

One or more enabled bits are set in the

Measurement Event register.