Renesas R61509V User Manual

Page 58

R61509V

Target

Spec

Rev. 0.11 April 25, 2008, page 58 of 181

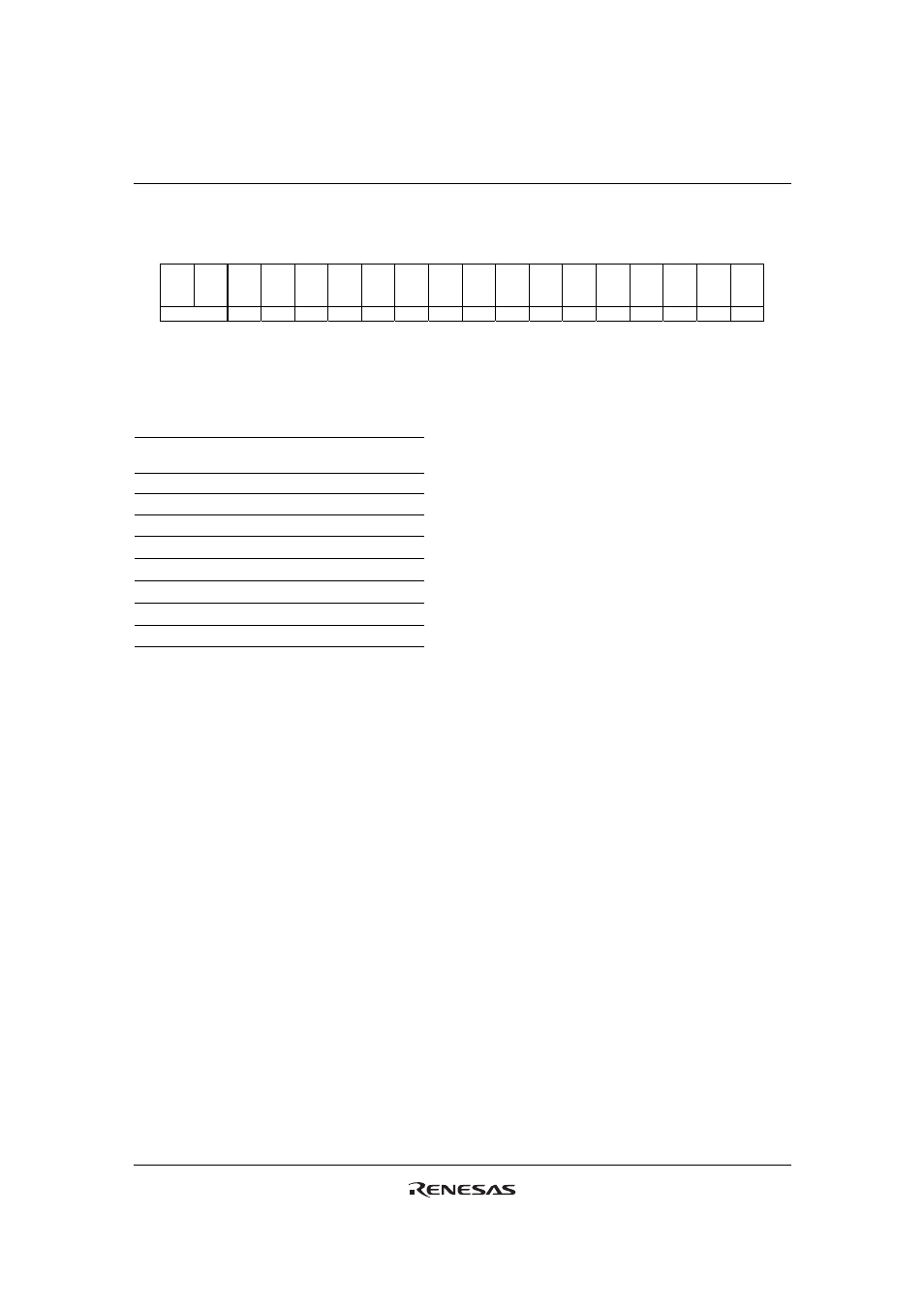

Panel Interface Control 4 (R013h)

MCPI: Defines VCOM alternating timing. This bit is enabled when displaying in synchronization with

internal clock. MCP cannot be used in RGB interface operation.

Table 28

MCPI [2:0]

VCOM alternating timing

3’h0

Setting inhibited

3’h1

1 clock

3’h2

2 clocks

3’h3 3

clocks

3’h4 4

clocks

3’h5 5

clocks

3’h6 6

clocks

3’h7 7

clocks

Note: The clock is the frequency divided clock, which is set by DIVI [1:0] bits.

R/W RS IB15 IB14 IB13 IB12 IB11 IB10 IB9

IB8

IB7

IB6

IB5

IB4

IB3 IB2 IB1 IB0

R/W

1 0 0 0 0 0 0 0 0 0 0 0 0 0

MC

PI[2]

MC

PI

[1]

MC

PI

[0]

Default

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1