Renesas R61509V User Manual

Page 126

R61509V

Target

Spec

Rev. 0.11 April 25, 2008, page 126 of 181

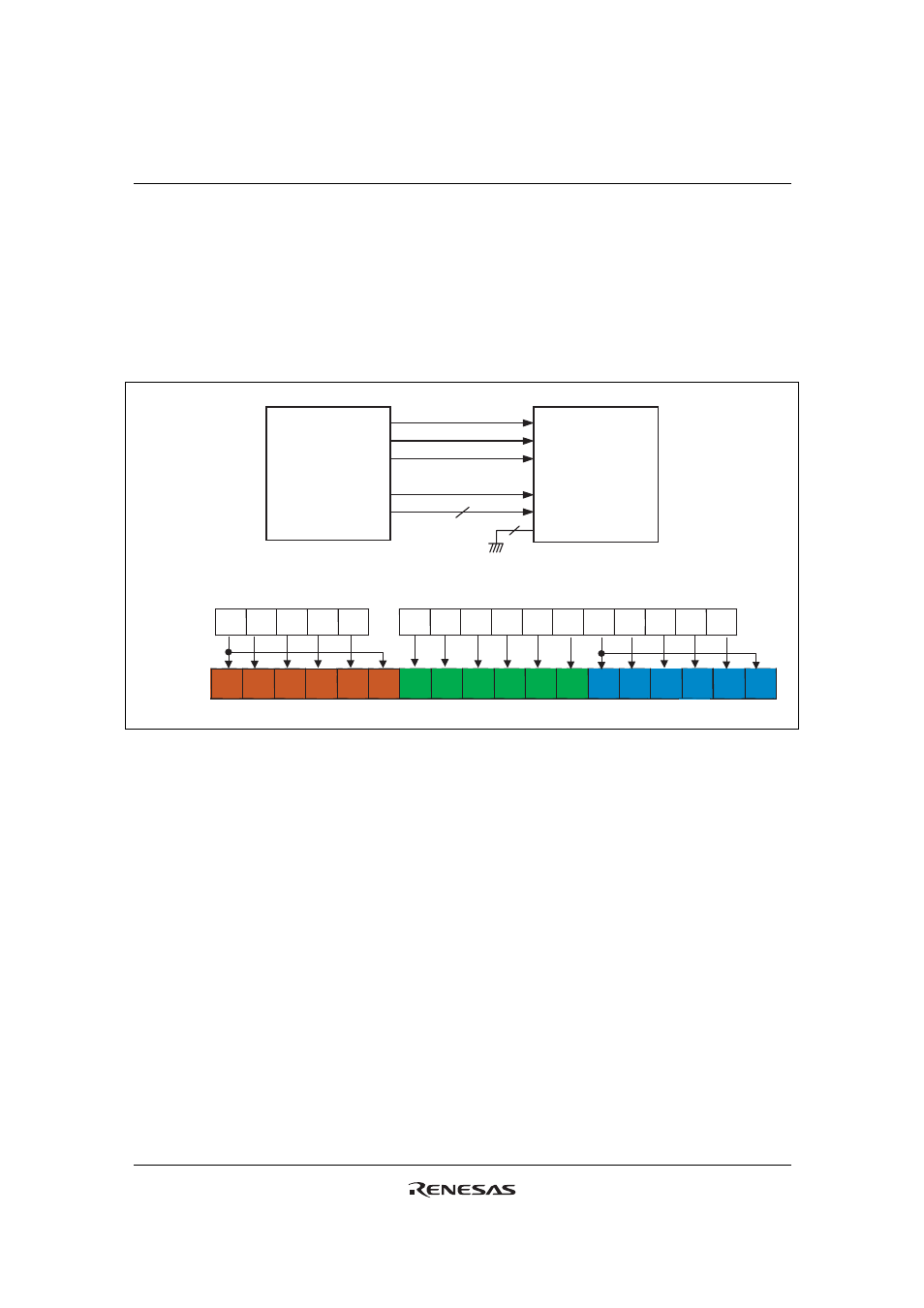

16-Bit RGB Interface

The 16-bit RGB interface is selected by setting RIM = 1. The display operation is synchronized with

VSYNCX, HSYNCX, and DOTCLK signals. The display data is transferred to the internal RAM in

synchronization with the display operation via 16-bit ports while data enable signal (ENABLE) allows

RAM access via RGB interface.

Instruction bits can be transferred only via system interface.

HOST

PROCESSOR

16

2

Input

DB

17

DB

16

DB

15

DB

14

DB

13

DB

11

DB

10

DB

9

DB

8

DB

7

DB

6

DB

5

DB

4

DB

3

DB

2

DB

1

DB17-13, 11-1

DB12,0

VSYNCX

HSYNCX

DOTCLK

ENABLE

R61509V

RIM = 1

Data format for the16-bit interface (RIM = 1)

R5

R4

R3

R2

R1

R0

G5

G4

G3

G2

G1

G0

B5

B4

B3

B2

B1

B0

Note: 65,536-color display

1 pixel

GRAM data

Figure 47 Example of 16-Bit RGB Interface and Data Format