Renesas M16C/6NM User Manual

Page 83

M306NKT-EPB User’s Manual

4. Hardware Specifications

REJ10J0519-0200 Rev.2.00 Oct. 16, 2006

Page 81 of 104

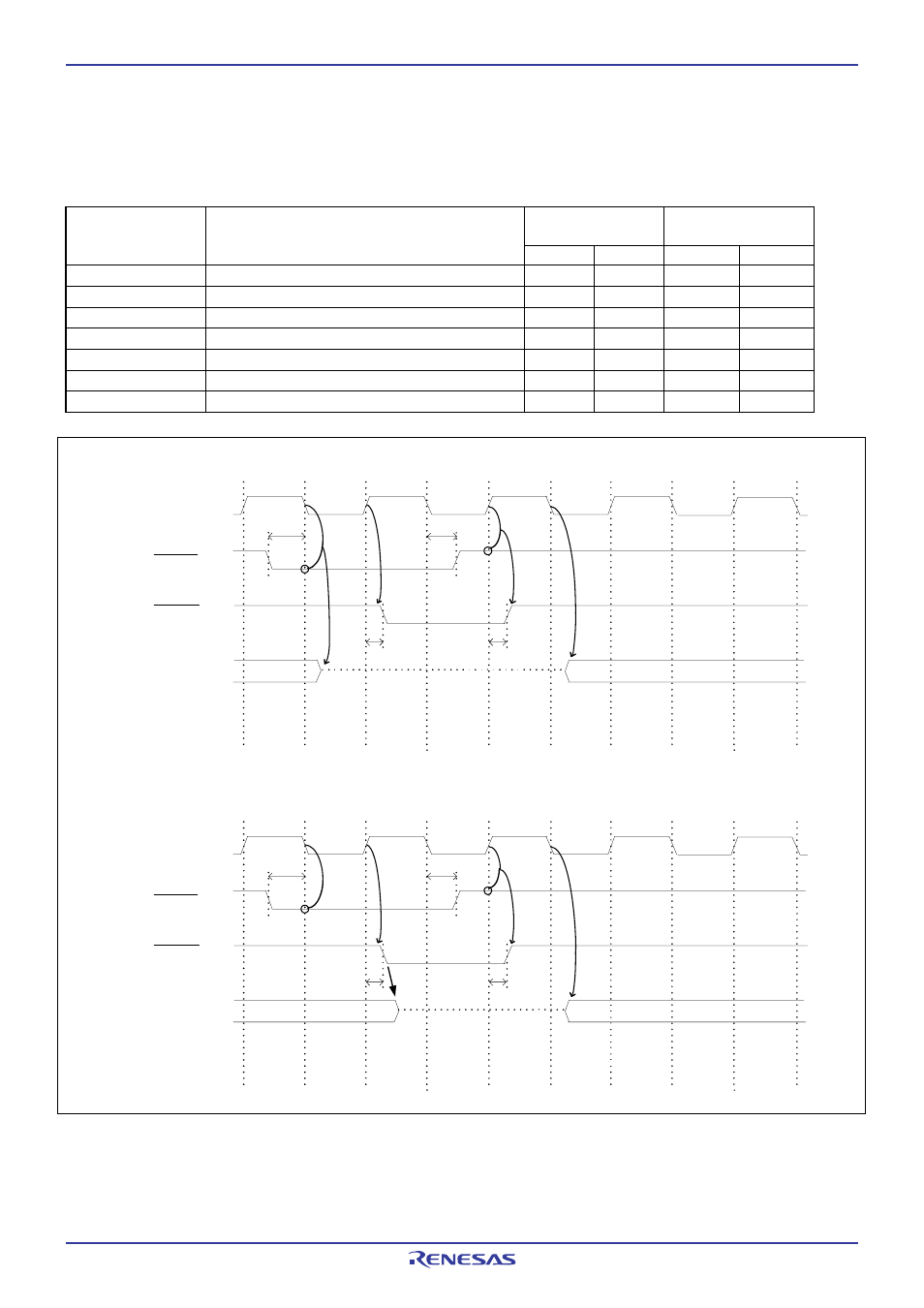

(3) Timing Requirements

Table 4.7 and Figure 4.6 show timing requirements in memory expansion mode and microprocessor mode.

Table 4.7 Timing requirements

Actual MCU

[ns]

This product

[ns]

Symbol Item

Min. Max. Min. Max.

tsu(DB-RD)

Data input setup time

50

65

tsu(RDY-BCLK)

RDY# input setup time

40

55

tsu(HOLD-BCLK)

HOLD# input setup time

50

65

th(RD-DB)

Data input hold time

0

See left

th(BCLK-RDY)

RDY# input hold time

0

See left

th(BCLK-HOLD)

HOLD# input hold time

0

See left

td(BCLK-HLDA)

HLDA# output delay time

40

See left

Figure 4.6 Timing requirements

* Compared with an actual MCU, this product enters high-impedance state after a 0.5 cycle delay.

Common to “with wait” and “no wait” (actual MCU)

H i -Z

BCLK

HOLD input

HLDA output

P0,P1,P2,P3,P4,

P5

0

- P5

2

tsu(HOLD-BCLK)

td(BCLK-HLDA)

td(BCLK-HLDA)

th(BCLK-HOLD)

Hi-Z

BCLK

HOLD input

HLDA output

P0,P1,P2,P3,P4,

P5

0

- P5

2

tsu(HOLD-BCLK)

td(BCLK-HLDA)

td(BCLK-HLDA)

th(BCLK-HOLD)

Common to “with wait” and “no wait” (this product)