Maxim Integrated DS33R11 User Manual

Page 244

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

244 of 344

Register Name:

TR.ESCR

Register Description:

Elastic Store Control Register

Register Address:

4Fh

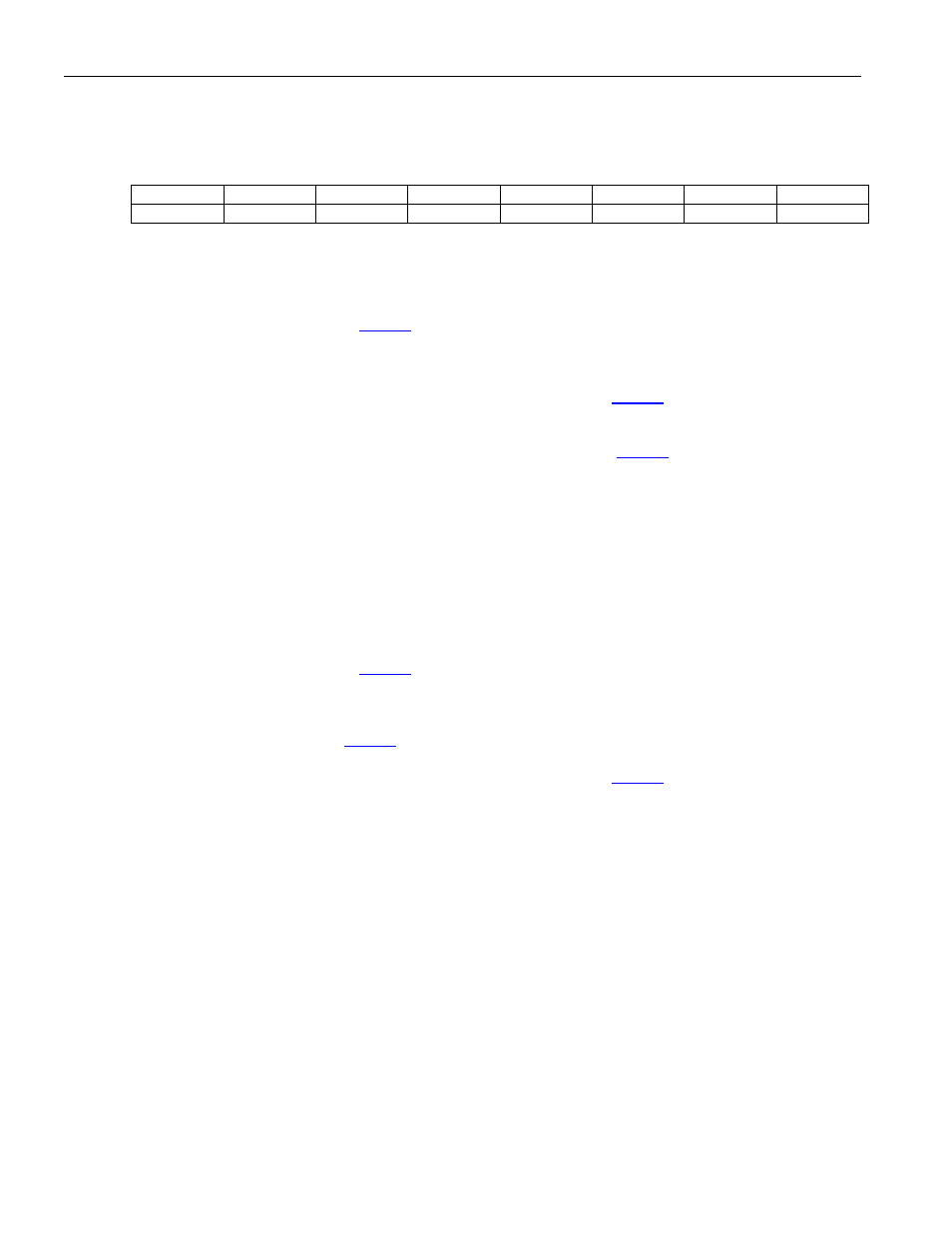

Bit

# 7 6 5 4 3 2 1 0

Name TESALGN TESR TESMDM TESE RESALGN

RESR RESMDM RESE

Default

0 0 0 0 0 0 0 0

Bit 7: Transmit Elastic Store Align (TESALGN). Setting this bit from a 0 to a 1 forces the transmit elastic store’s

write/read pointers to a minimum separation of half a frame. No action is taken if the pointer separation is already

greater or equal to half a frame. If pointer separation is less than half a frame, the command is executed and the

data is disrupted. It should be toggled after TSYSCLK has been applied and is stable. It must be cleared and set

again for a subsequent align. See Section

Bit 6: Transmit Elastic Store Reset (TESR). Setting this bit from a 0 to a 1 forces the read and write pointers into

opposite frames, maximizing the delay through the transmit elastic store. Transmit data is lost during the reset. It

should be toggled after TSYSCLK has been applied and is stable. See Section

for details. Do not leave

this bit set HIGH.

Bit 5: Transmit Elastic Store Minimum-Delay Mode (TESMDM). See Section

for details.

0 = elastic stores operate at full two-frame depth

1 = elastic stores operate at 32-bit depth

Bit 4: Transmit Elastic Store Enable (TESE)

0 = elastic store is bypassed

1 = elastic store is enabled

Bit 3: Receive Elastic Store Align (RESALGN). Setting this bit from a 0 to a 1 forces the receive elastic store’s

write/read pointers to a minimum separation of half a frame. No action is taken if the pointer separation is already

greater or equal to half a frame. If pointer separation is less than half a frame, the command is executed and the

data is disrupted. It should be toggled after RSYSCLK has been applied and is stable. Must be cleared and set

again for a subsequent align. See Section

Bit 2: Receive Elastic Store Reset (RESR). Setting this bit from a 0 to a 1 forces the read and write pointers into

opposite frames, maximizing the delay through the receive elastic store. It should be toggled after RSYSCLK has

been applied and is stable. See Section

for details. Do not leave this bit set HIGH.

Bit 1: Receive Elastic Store Minimum-Delay Mode (RESMDM). See Section

for details.

0 = elastic stores operate at full two-frame depth

1 = elastic stores operate at 32-bit depth

Bit 0: Receive Elastic Store Enable (RESE)

0 = elastic store is bypassed

1 = elastic store is enabled