Maxim Integrated DS33R11 User Manual

Page 203

DS33R11 Ethernet Mapper with Integrated T1/E1/J1 Transceiver

203 of 344

Register Name:

TR.IOCR2

Register Description:

I/O Configuration Register 2

Register Address:

02h

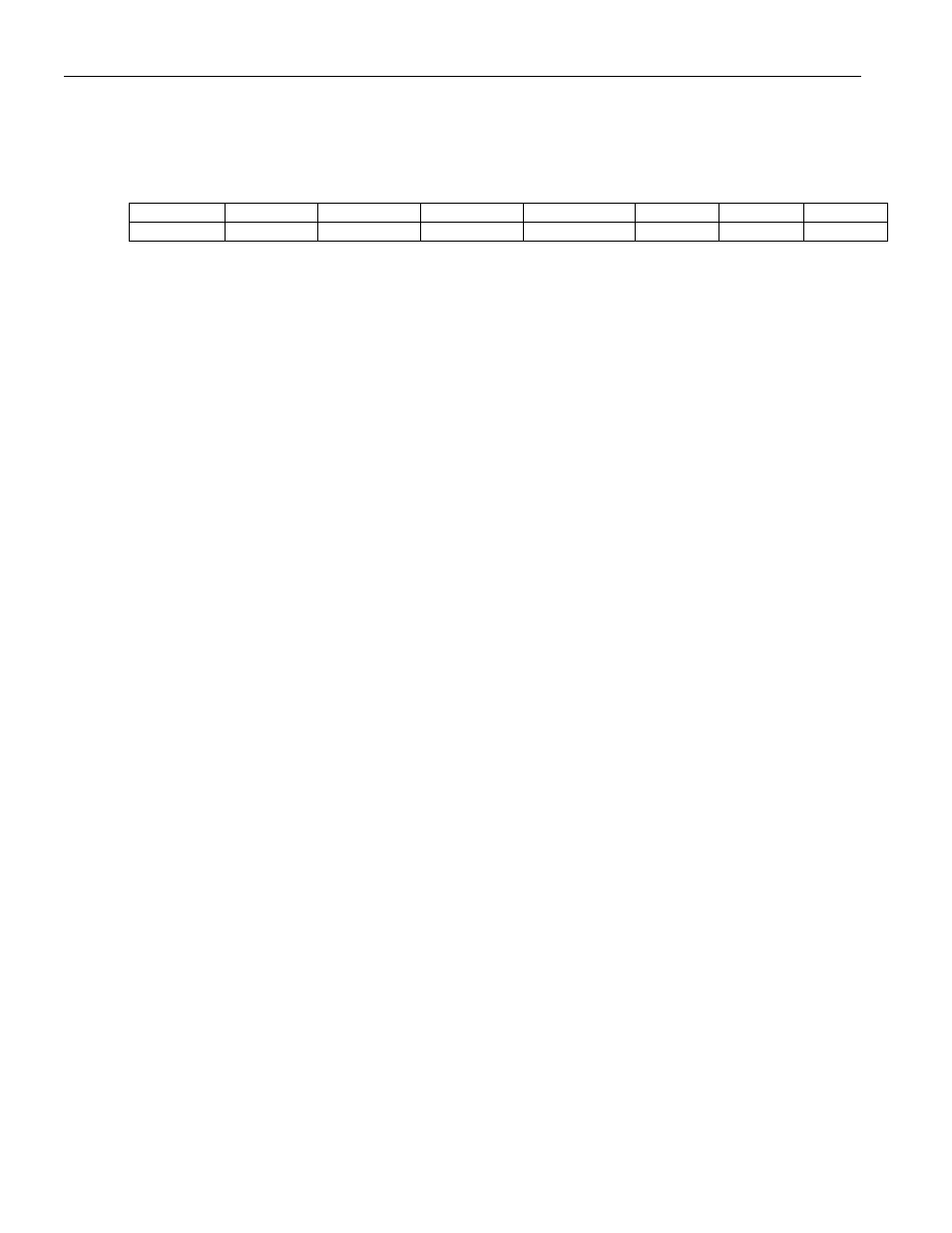

Bit

#

7 6 5 4 3 2

1

0

Name RCLKINV TCLKINV

RSYNCINV

TSYNCINV TSSYNCINV H100EN TSCLKM RSCLKM

Default

0 0 0 0 0 0

0

0

Bit 7: RCLKO Invert (RCLKINV)

0 = no inversion

1 = inverts signal on RCLKO output.

Bit 6: TCLKT Invert (TCLKINV)

0 = no inversion

1 = inverts signal on TCLKT input.

Bit 5: RSYNC Invert (RSYNCINV)

0 = no inversion

1 = invert

Bit 4: TSYNC Invert (TSYNCINV)

0 = no inversion

1 = invert

Bit 3: TSSYNC Invert (TSSYNCINV)

0 = no inversion

1 = invert

Bit 2 : H.100 SYNC Mode (H100EN)

0 = normal operation

1 = SYNC shift

Bit 1: TSYSCLK Mode Select (TSCLKM)

0 = if TSYSCLK is 1.544MHz

1 = if TSYSCLK is 2.048MHz

Bit 0: RSYSCLK Mode Select (RSCLKM)

0 = if RSYSCLK is 1.544MHz

1 = if RSYSCLK is 2.048MHz